Géné VHF 1Hz à 100MHz à DDS AD9951 piloté par GPS

Le but de cette étude n'est pas de réaliser un émetteur de radio mais un générateur de laboratoire de très faible puissance (<1mW c.a.d < 0 dBm), permettant d'expérimenter et de régler des circuits VHF comme des filtres par exemple, afin de confronter la théorie à l'expérience, sans rayonner. L'appareil doit être enfermé dans un boîtier métallique relié à la masse. La sortie du signal se fera sur une prise BNC. Un filtre VHF sera intercalé sur l'alimentation.

Voir les liens en bas de page concernant l'attribution des fréquences radio. Toute émission dans les bandes VHF est interdite (hors bande radio-amateur) et serait rapidement repérée ce qui peut vous amener directement en prison.

A la rigueur les radio-amateurs en possession de la licence et ayant des connaissances en électronique et en VHF pourront envisager d'adapter cette réalisation pour leurs besoins propres.

Cette étude fait suite à celle du générateur 40MHz à DDS AD9850 décrit sur ce site.

Cliquez sur une image ci-dessous pour visualiser l'album. Certaines sont commentées

1 Première approche

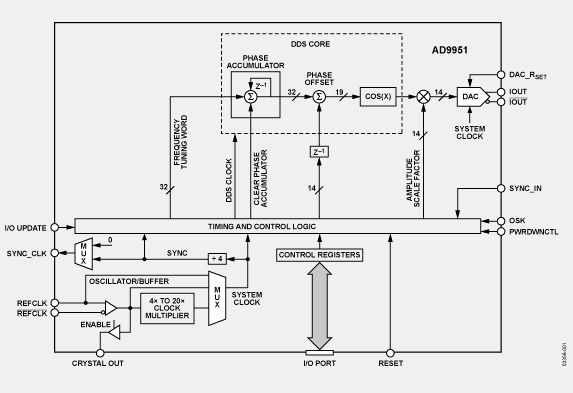

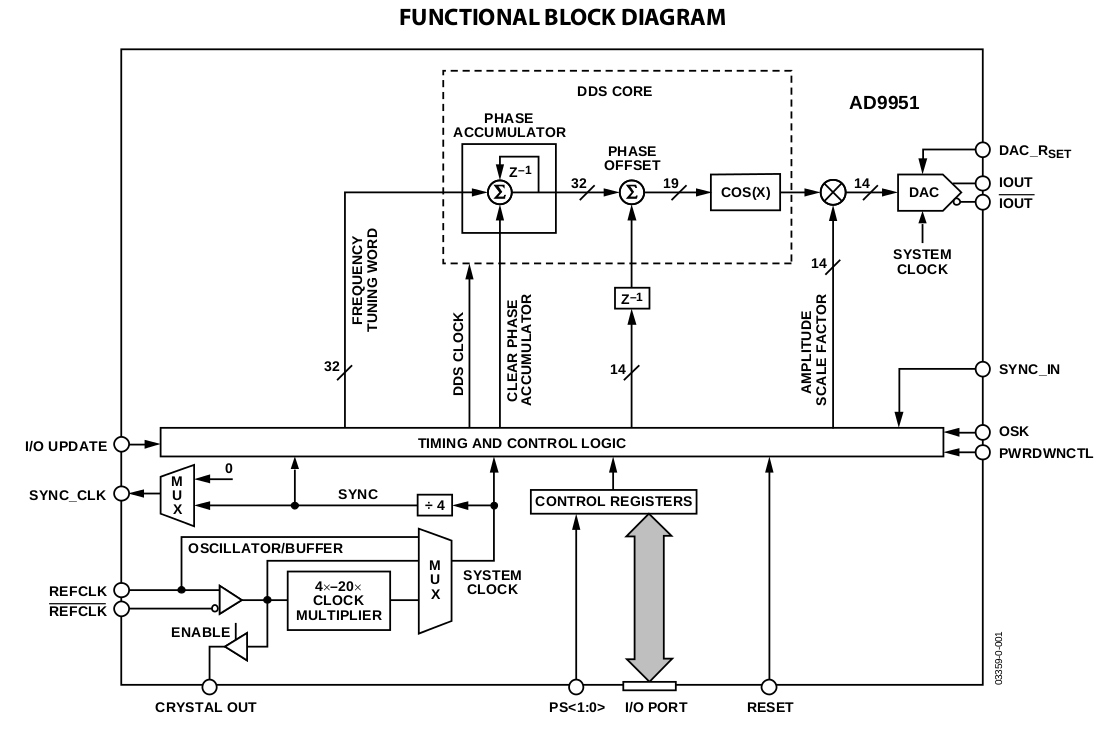

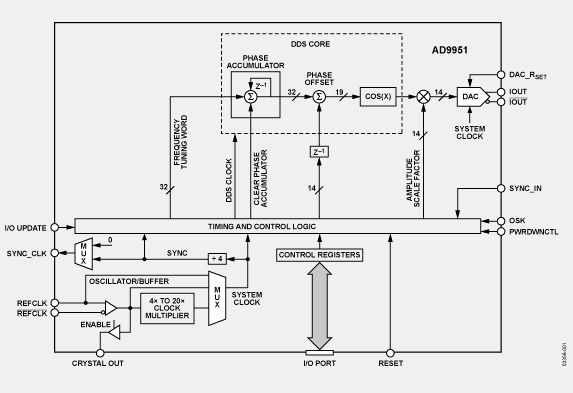

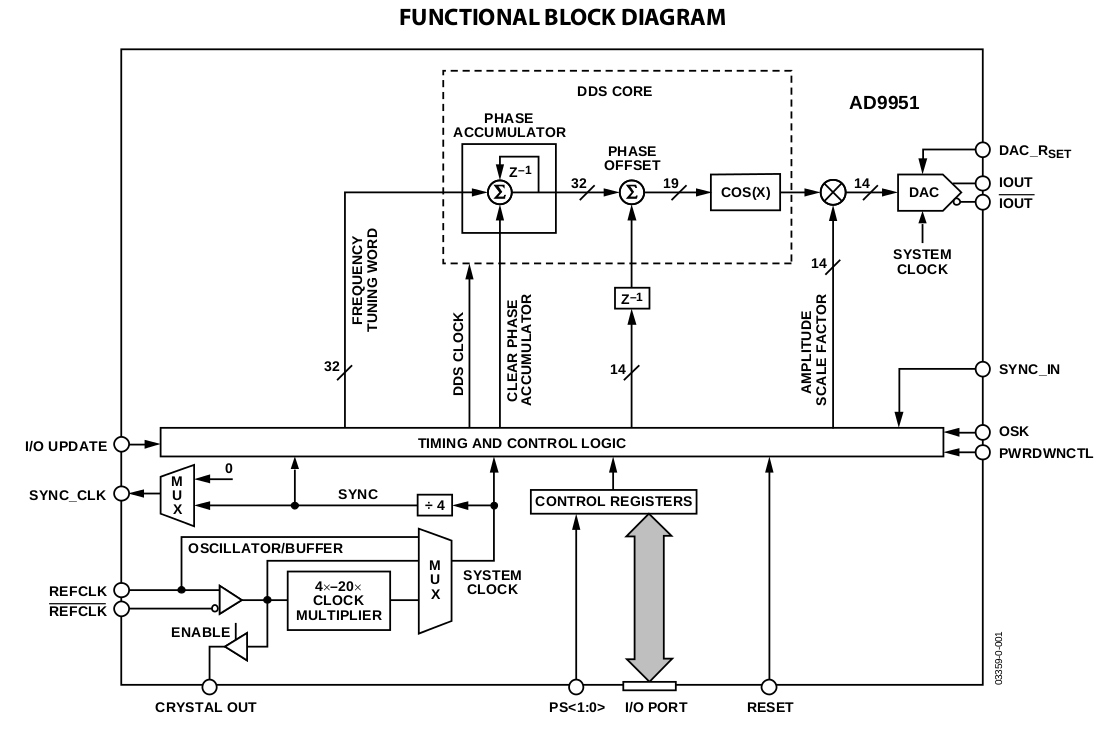

29 août 2014: J'ai commencé par le commencement, l'étude du datasheet du composant principal, le circuit DDS AD9951 de Analog Device.

Puis j'ai commandé le circuit.

|

|

|

|

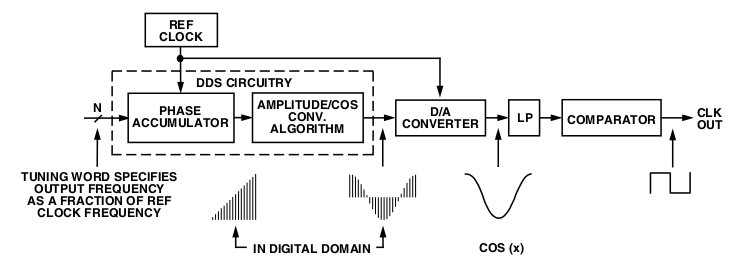

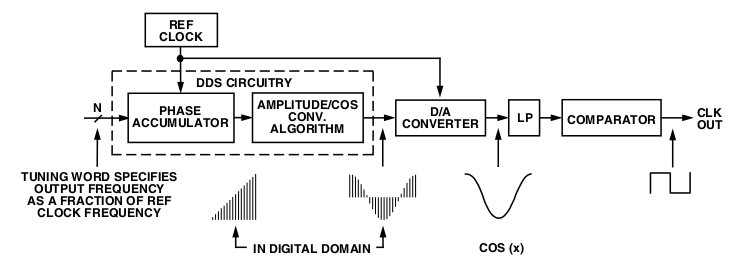

2 Un peu de théorie :

La circuiterie interne du DDS est un diviseur digital de fréquence dont la résolution incrémentale (la finesse du pas) est déterminée par la fréquence de l'horloge de référence (ici 200 MHz) divisée la 2^N nombre de bits du mot de commande de fréquence (un grand (32 bits) nombre binaire qui détermine la fréquence de sortie).

L'accumulateur (la mémoire) de phase est un compteur à module variable qui incrémente (ajoute) le nombre enregistré à chaque fois qu'il reçoit une impulsion d'horloge.

Lorsque le compteur déborde, il reboucle sur lui-même de sorte que le signal est généré continuellement.

Le mot de commande de fréquence (il sera fourni par l'ATmega en fonction de la fréquence désirée) constitue la valeur du module du compteur, ce qui en fin de compte détermine la taille de l'incrément (delta phase) qui est ajouté dans l'accumulateur de phase lors de l'impulsion d'horloge suivante. Plus l'incrément est large et plus vite l'accumulateur se remplit et déborde ce qui produit une fréquence plus élevée. Le signal numérique de sortie est issu d'un calcul mathématique d'une fonction cosinus avec comme variable la valeur de la phase.

|

|

|

|

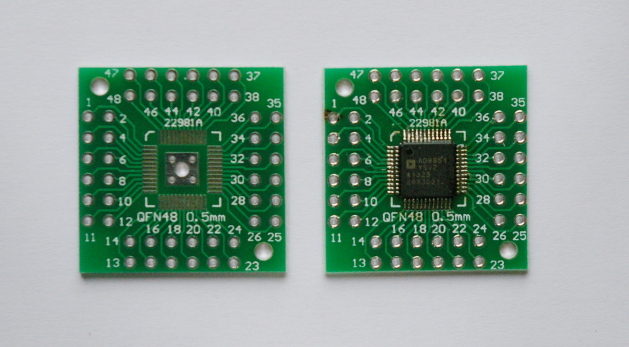

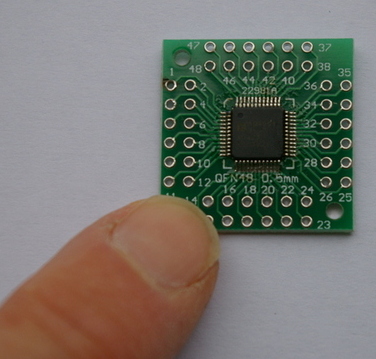

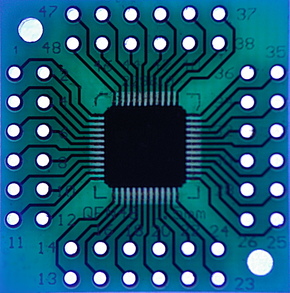

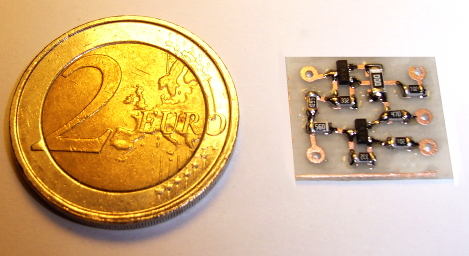

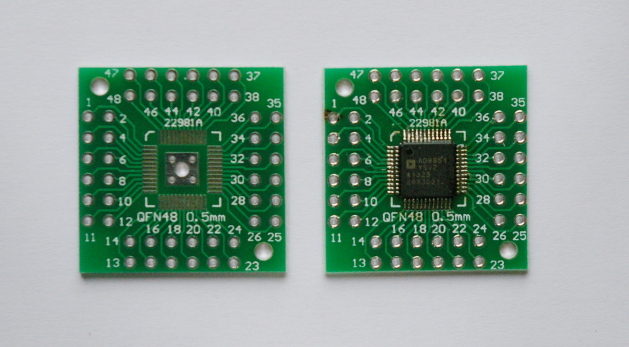

3 Premier contact avec le circuit AD9951

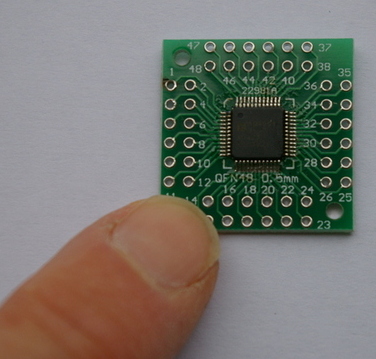

|

Réception du circuit... Boudiouuu c'est tout petit ! Le boitier est un QFP48 au pas de 0.5mm. Heureusement j'avais en même temps commandé un adaptateur QFP48 -> DIP sur lequel j'ai réussi à souder l'AD9951. Un partie de plaisir quand on sait faire ! (y'a un truc !)

Bon d'accord, sur le plan HF l'utilisation de cet adaptateur ne va pas optimiser les performances, il faudra souder les capas de découplage des alims 1.8V et 3.3V au plus près du boîtier. Mais il s'agit pour l'instant de réaliser un prototype qui permette de mettre au point le programme pilote. Je vais utiliser un ATmega8 pour driver ce DDS et un affichage LCD 4x20.

|

|

|

|

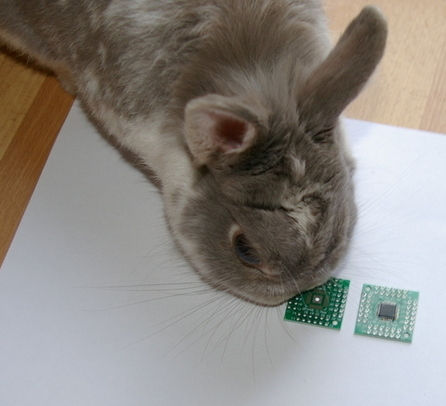

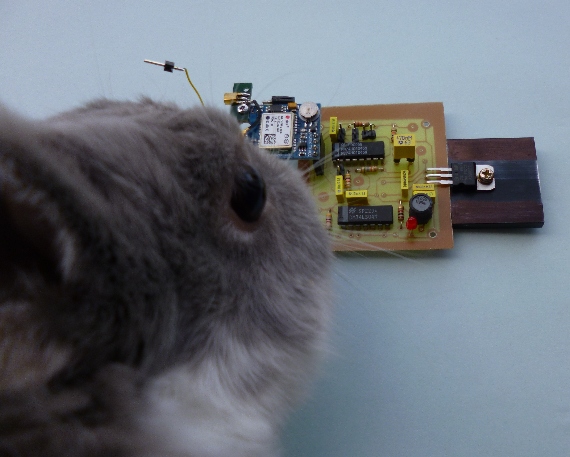

4 Skippy est très intéressé !

|

|

|

|

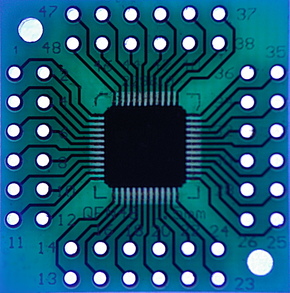

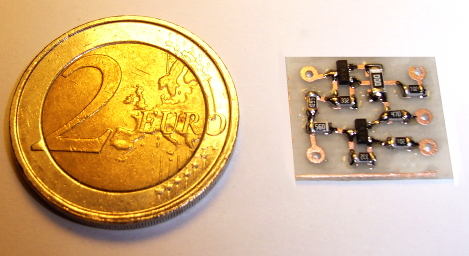

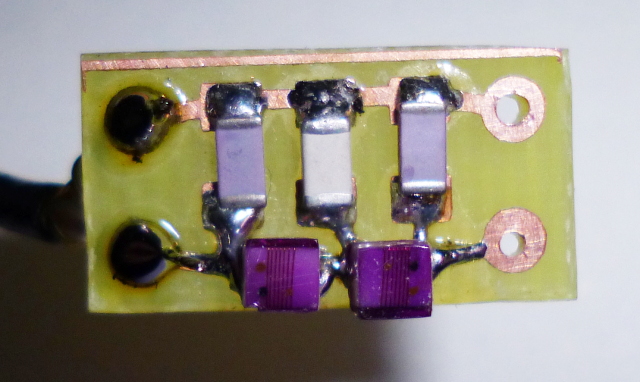

5 La soudure du boitier CMS

|

Après soudure, il convient de vérifier soigneusement l'absence de courts circuits entre les pattes, par transparence et à la loupe. Je déconseille l'utilisation de l’ohmmètre étant donné que la partie analogique de ce circuit fonctionne avec une tension très faible de 1,8V.

|

|

|

|

6 soudure ok

|

|

|

|

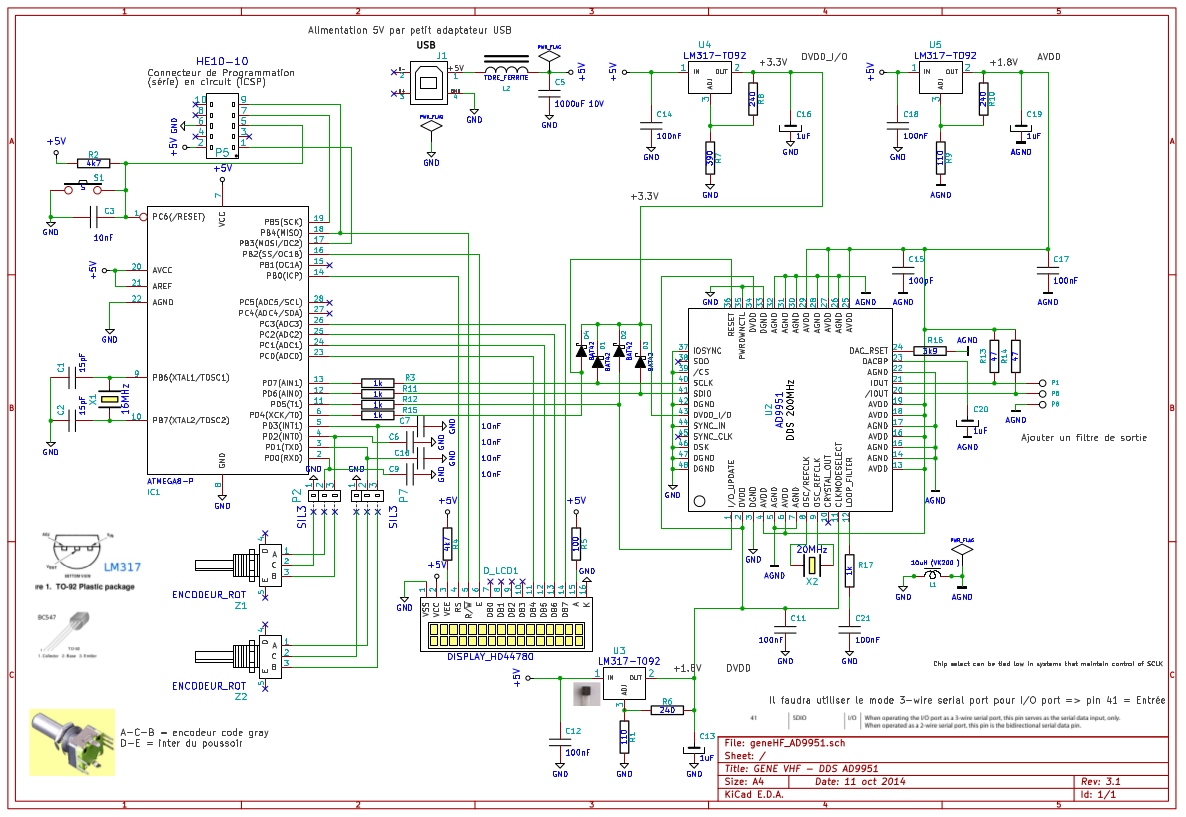

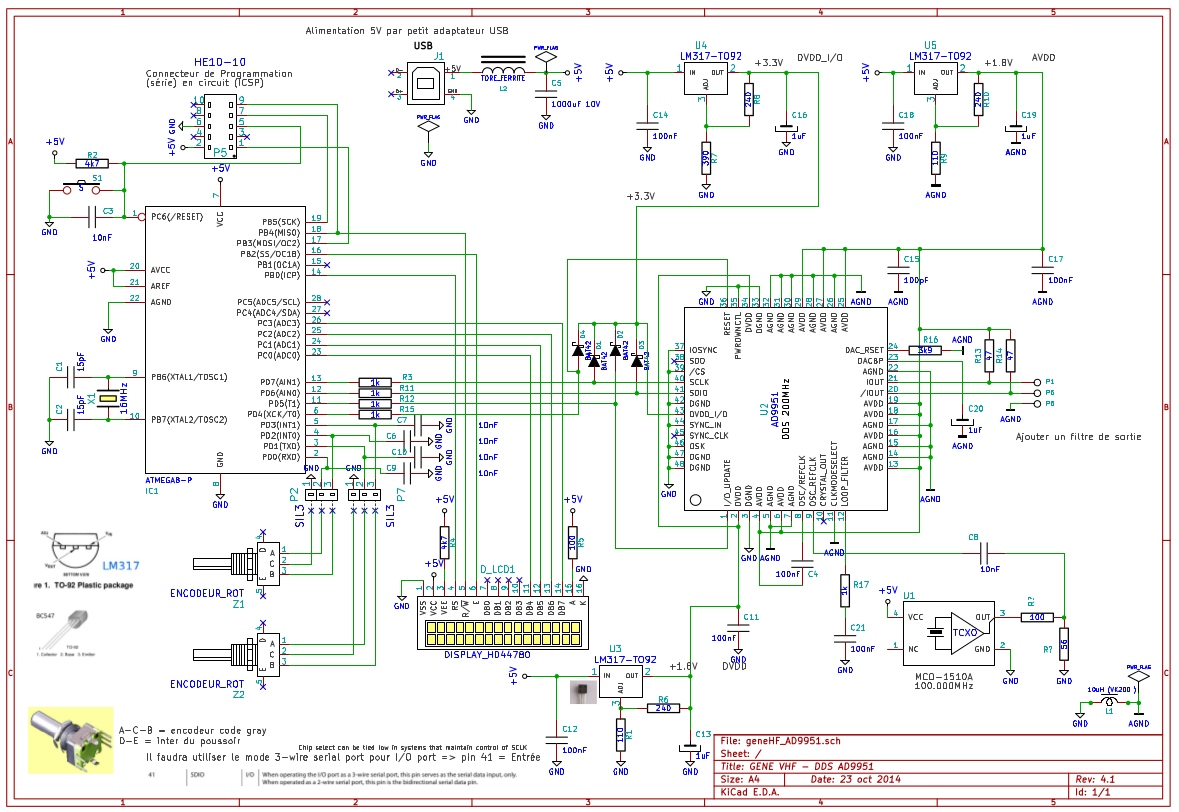

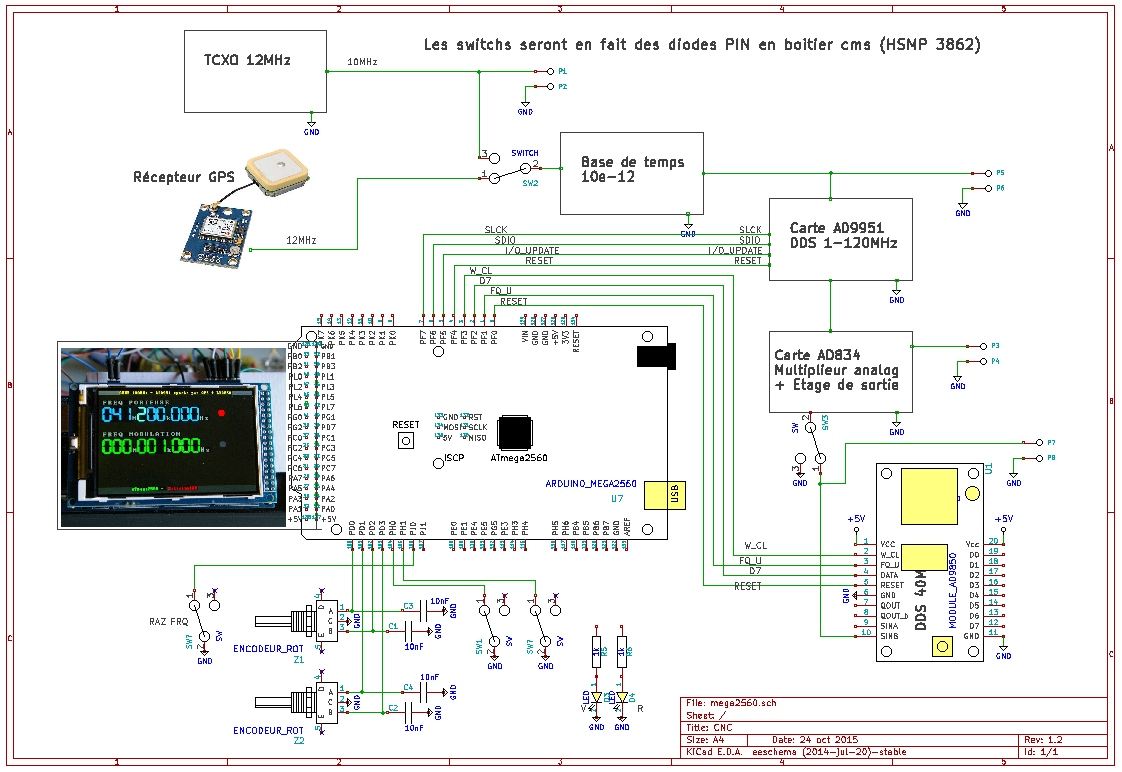

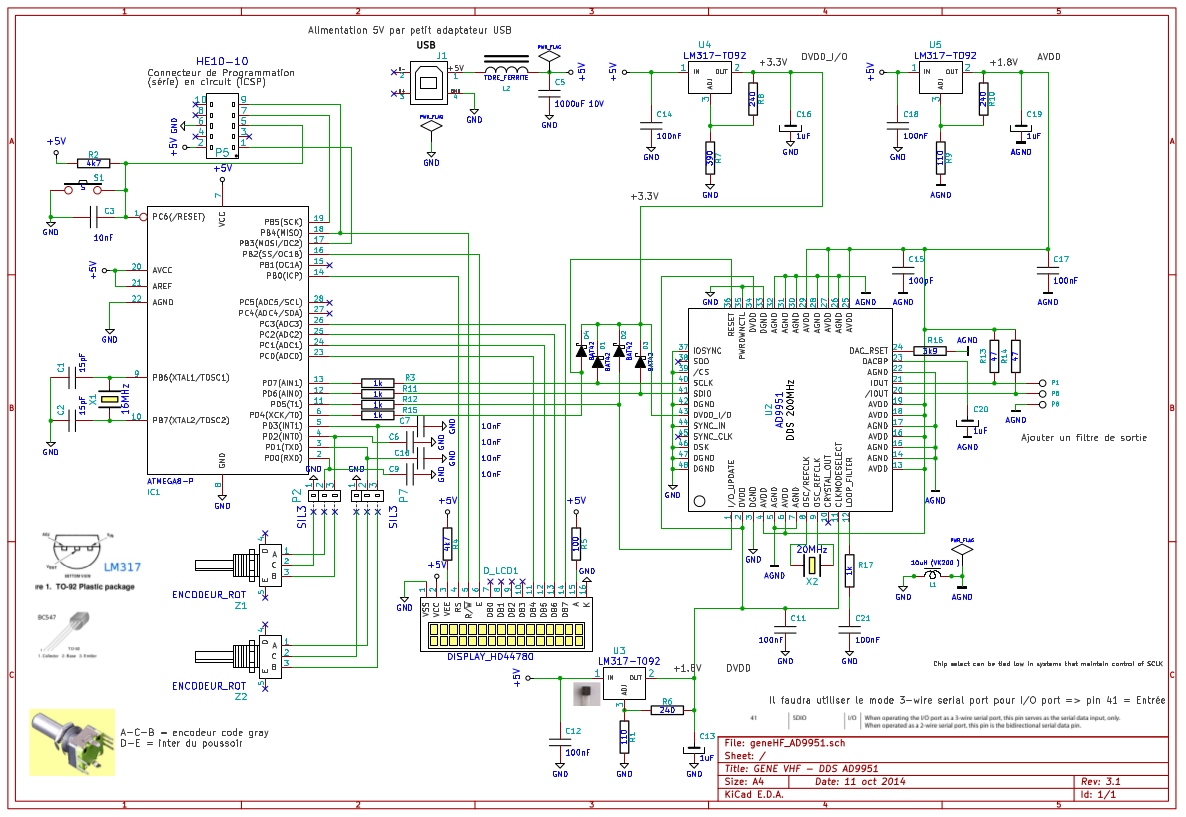

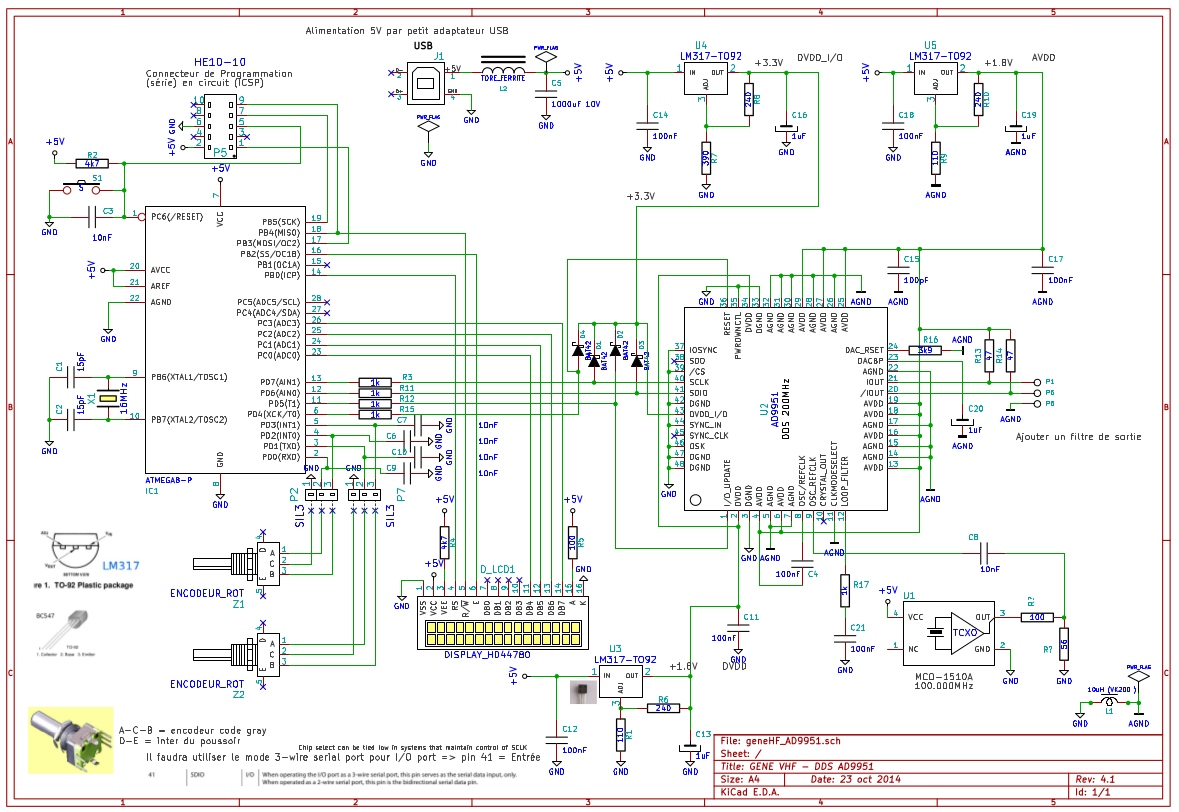

7 Le schéma

La saisie de la fréquence désirée se fait par deux encodeurs pas-à-pas rotatifs code Gray. J'ai consacré un article à cette méthode sur ce site.

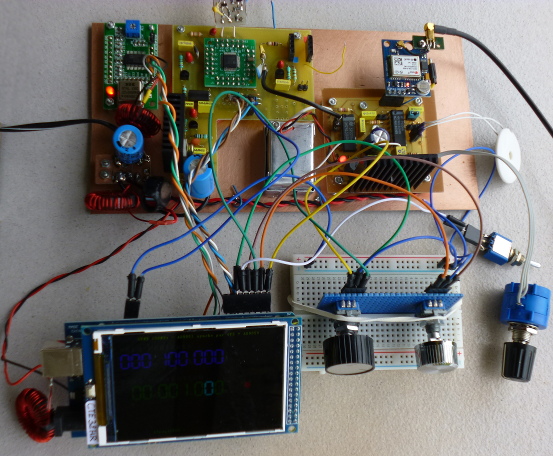

L'interface logique du DDS s'alimente en 3,3V et la partie analogique ainsi que le convertisseur CAN interne en 1,8V. La documentation conseille d'utiliser deux régulateurs séparés pour les deux alims de 1,8V.

Quatre résistances de 1k + diodes schottky réalise l'interface entre les ports en sortie 5V de l'ATmega (because l'affichage en 5V) et les entrées data en 3,3V du DDS.

La sortie du CAN est un géné de courant en mode différentiel. Les deux R de 47 ohm permettent de récupérer des tensions symétriques.

L'ensemble est alimenté par un "adaptateur USB" délivrant 5V DC. Certains "adaptateurs" fournissent une tension pleine de parasites (découpage mal filtré)

voire une composante 50Hz non négligeable. D'où la self et le 1000uF en entrée.

|

|

|

|

8 Le firmware pour l'ATmega8

|

|

|

|

|

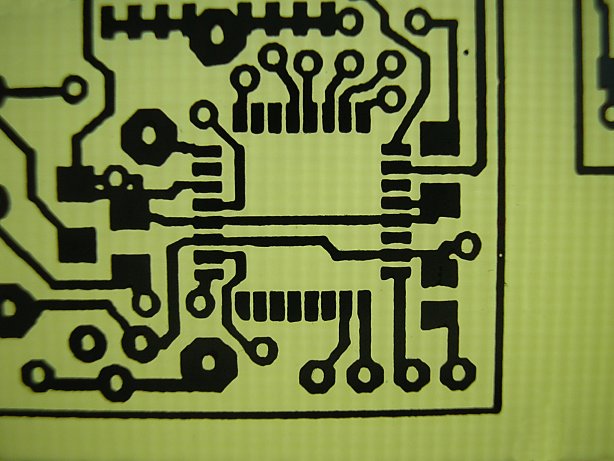

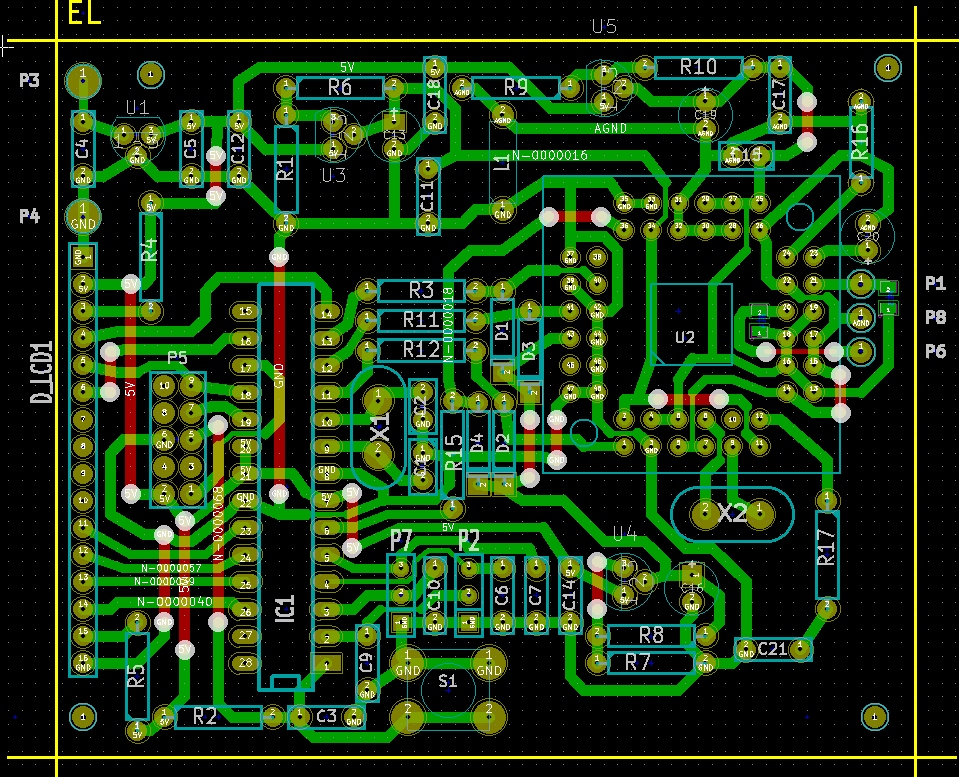

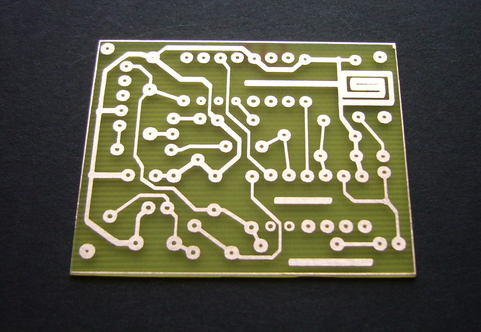

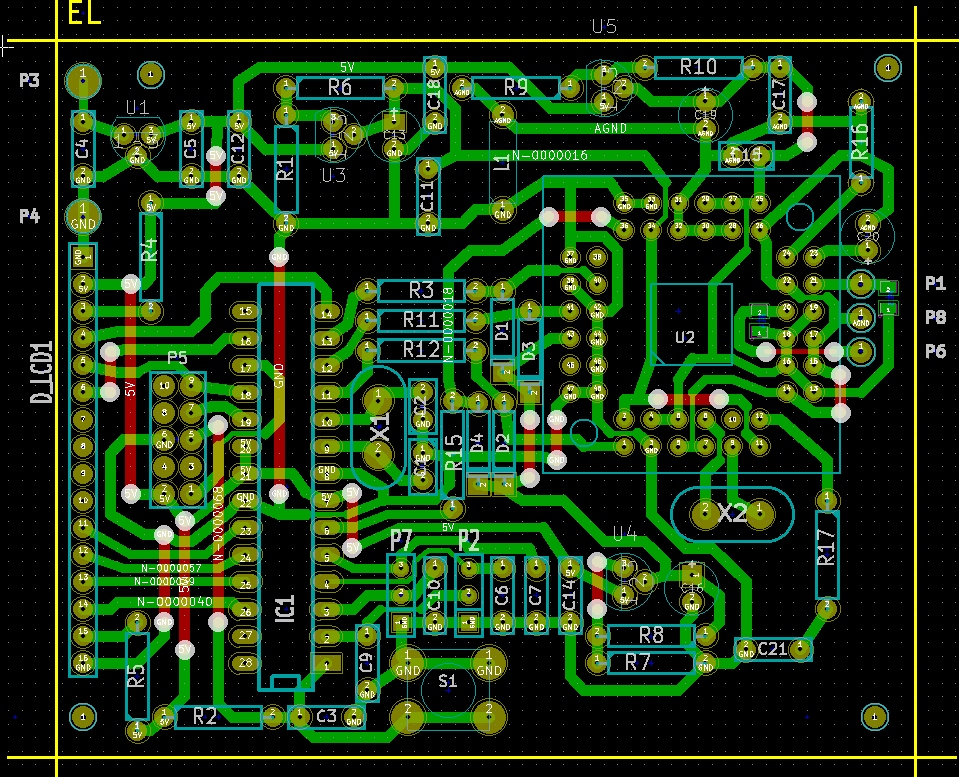

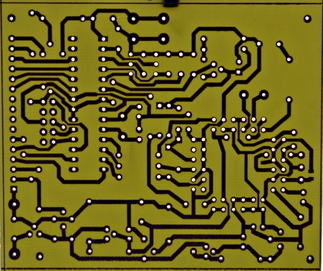

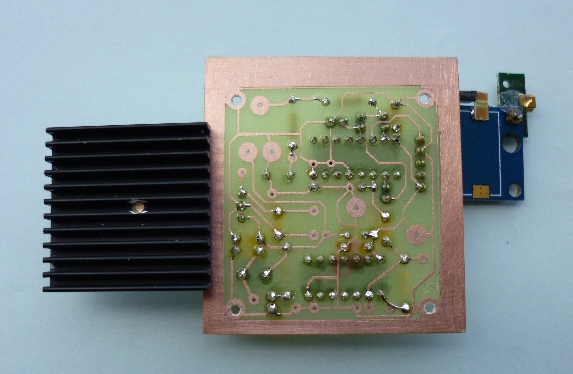

9 Dessin du circuit imprimé

| |

|

|

|

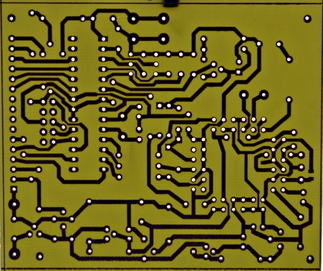

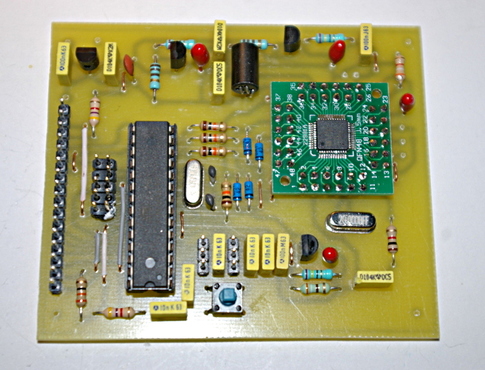

10 Réalisation du circuit imprimé

|

06 setp 2014:

Le circuit imprimé est fait, il ne reste plus qu'à souder les composants...

|

|

|

|

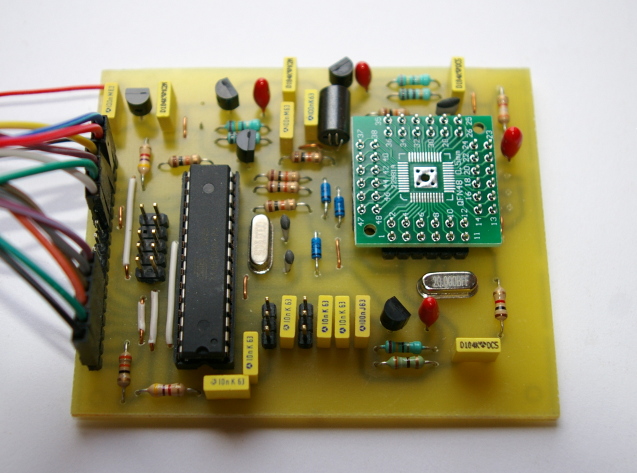

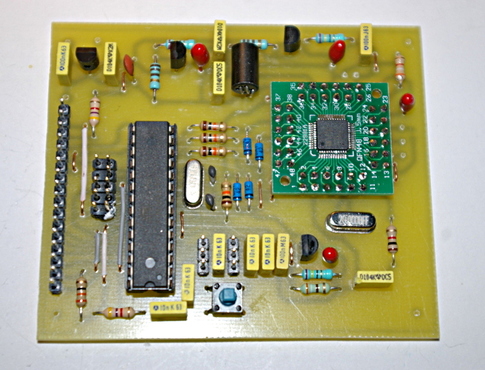

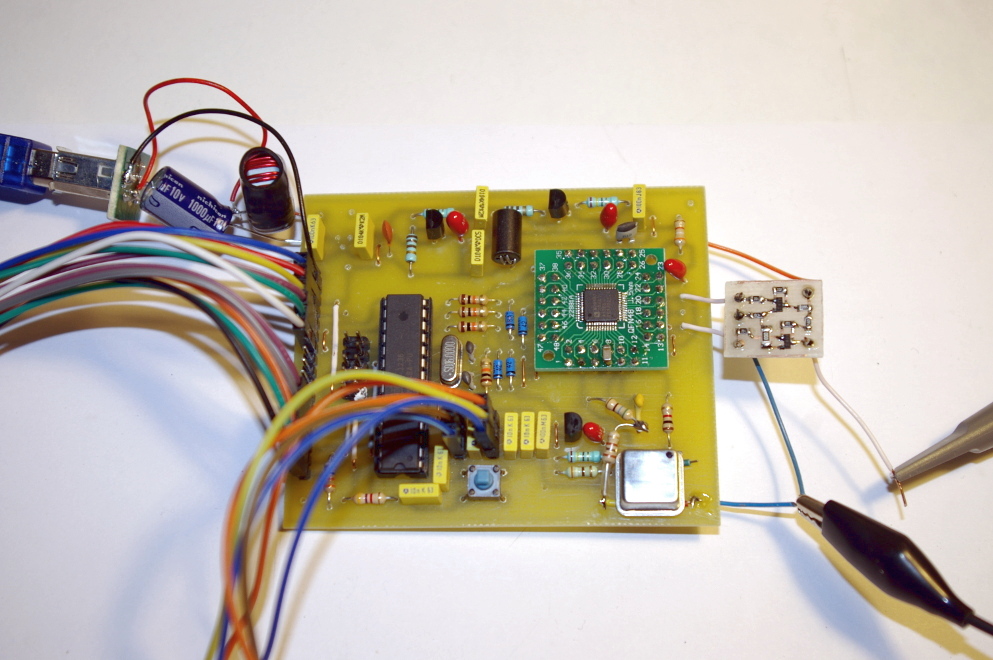

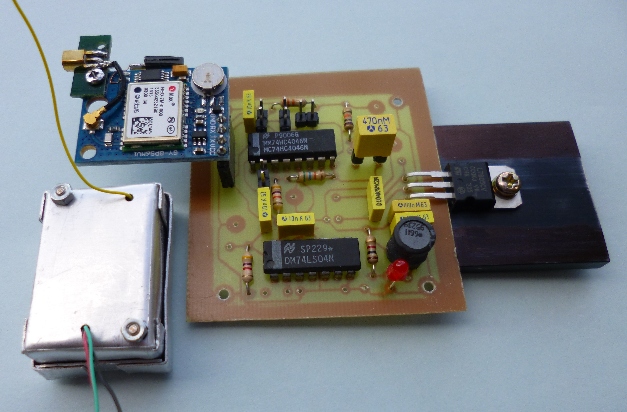

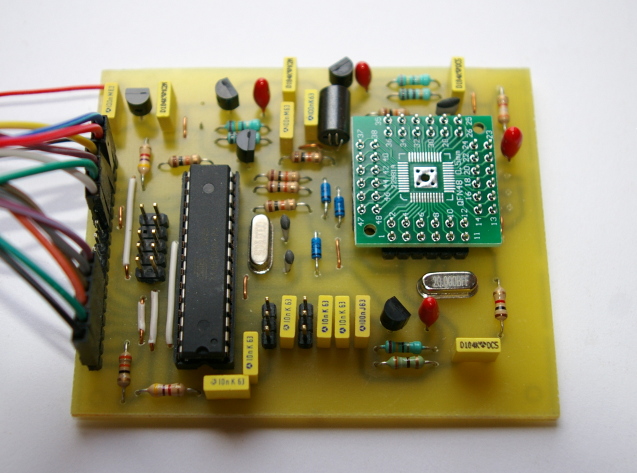

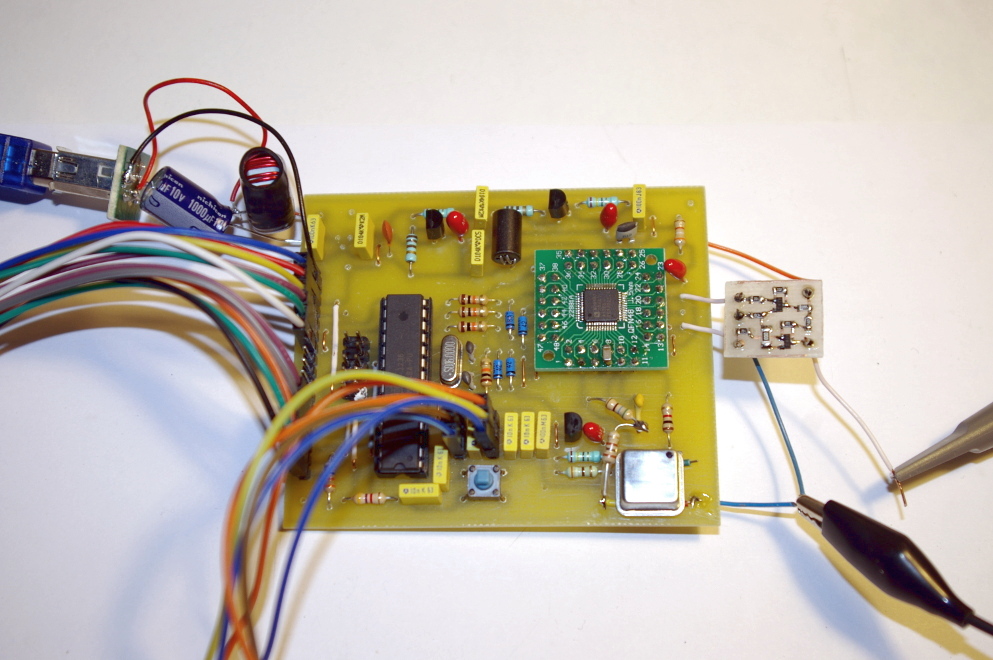

11 Carte terminée :

|

08 sept 2014:

Les composants sont soudés, sauf la platine AD9951 (celle en place ne comporte pas de circuit).

J'ai ainsi pu tester les alims 5V, 3.3V, 1.8V et leur présence sur les pins correspondants.

|

|

|

|

12 Le DDS est en place sur la carte

|

|

|

L'ATmega, les boutons codeurs et l'affichage fonctionnent correctement. Je dispose donc d'une platine d'expérimentation complète qui va me permettre de développer le soft qui pilotera l'AD9951.

La partie la plus intéressante commence donc maintenant.

|

13 Premier signal !

|

12 sept 2014:

Eurêka ! L'AD9951 vient de générer pour la première fois des signaux sinusoïdaux dans une gamme étendue de fréquence (de qq HZ à qq dizaines de MHz).

Ouf ! Il était temps. Il m'a juste rendu fou pendant deux jours !! Certains points ne sont pas clairs dans le datasheet. En particulier l'application du signal I/O_UPDATE pour un DDS unique.

Je vais maintenant pouvoir le piloter précisément et lui faire générer la fréquence exacte désirée. Et bien entendu je publierai tous les codes sources en C ici.

|

|

|

|

14 Tout fonctionne correctement !

13 sept 2014:

Tout fonctionne correctement. La saisie de la fréquence (et du pas) par les boutons codeurs rotatifs est opérationnelle, la fréquence de sortie réagit instantanément.

Il reste à:

- vérifier le comportement au delà de ce que j'ai testé avec un oscillo 30MHz ( donc oscillo 100MHz puis analyseur de spectre 1GHz).

- concevoir un étage de sortie sérieux (actuellement les signaux de sorties sont en mode différentiel à très bas niveau), assorti d'un filtre VHF.

- re-test à l'analyseur de spectre

- mise en boitier

- re-re-test à l'analyseur de spectre

|

|

|

|

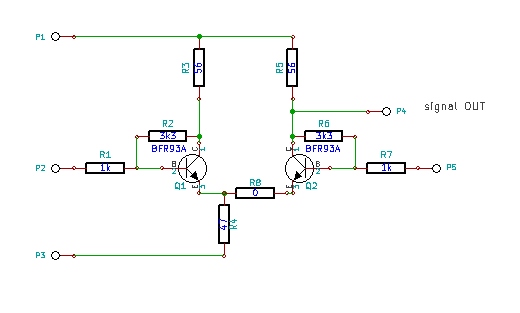

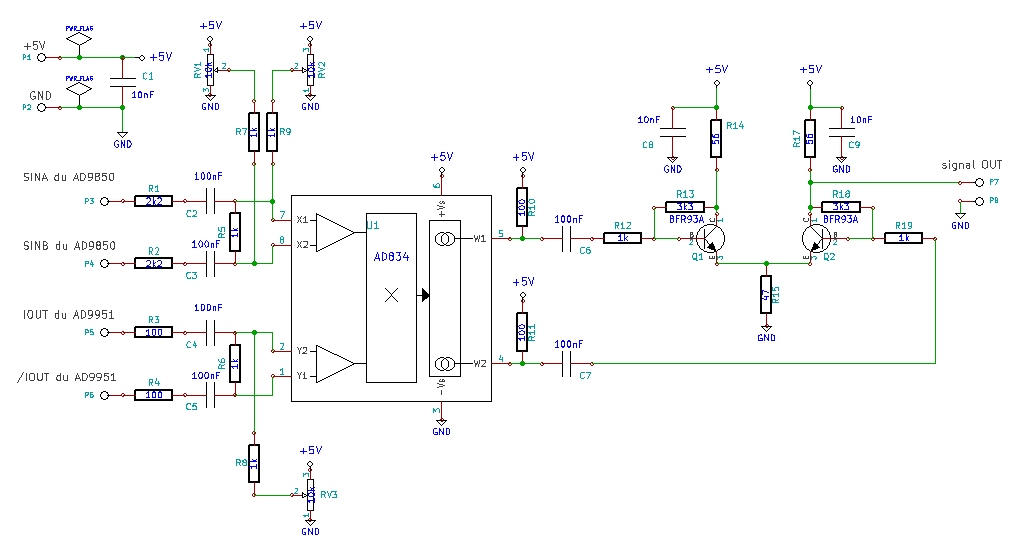

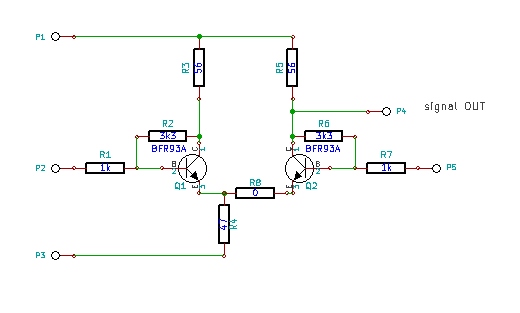

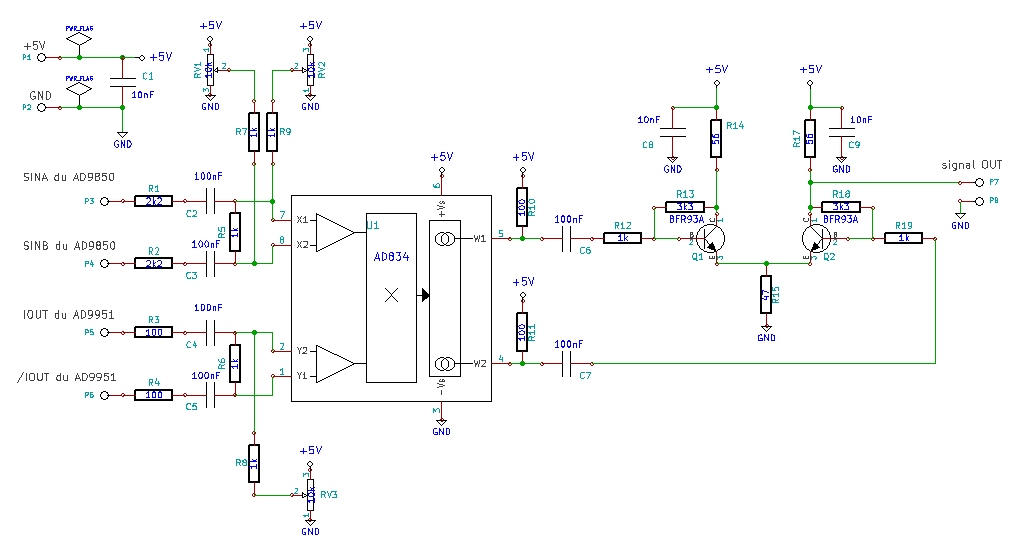

15 Etage de sortie

10 octobre 2012:

Après avoir délaissé cette réalisation pendant un mois, je m'y suis replongé depuis hier et j'ai mis au point un étage de sortie qui délivre 1V crête à crête jusqu'à la fréquence maximum que j'ai pu visualiser et mesurer, soit 160 MHz.

Mais auparavant je vous dis le pourquoi de ce mois de retard. Une lecture attentive de ce site vous montrera que pendant ce temps j'ai réparé mon oscilloscope HM303-4. Mais ce n'est pas la vraie raison. En fait j'ai opéré cette modification sur mon oscillo (qui en avait certainement besoin) pour... passer le temps !

Tiens donc, monsieur joue alors que les choses sérieuses attendent ! Ben c'est à dire que la chose sérieuse en question ne marchait plus ! Ah ? et pourquoi ? Ben parce que j'avais grillé l'AD9951 !!!! Et de la manière la plus idiote qui soit ! J'ai voulu faire une vidéo de la carte en fonctionnement, posée sur l'oscilloscope avec dans le champ le fréquencemètre, et le camescope sur un pied photo. ça fonctionnait correctement puis clac, d'un coup plus rien, même l'affichage et l'Atmega se sont éteints.

Il se trouve que j'avais soudé un petit bout de fil de 5 cm sur une des sorties de l'AD9951 pour y connecter la sonde de l'oscillo. Et dans l'installation bancale pour la prise de vue, ce point non isolé sur une longueur d'environ 1mm a trouvé le moyen d'aller toucher l'alimentation générale de la carte, soit 8V 2A. Je confirme que l'AD9951 fonctionnant à 1,8V n'a pas apprécié. Quant au mois d'attente, c'est le temps de recevoir un circuit tout neuf commandé à Hong Kong.

Bref, voici le schéma de l'étage de sortie :

|

|

|

|

16 Schéma de l'étage de sortie

|

|

|

La fonction de cet étage de sortie N'EST PAS d'obtenir un signal puissant.

Le but est de fournir un signal propre (sinusoïdal) d'amplitude juste deux fois plus grande (1V crête à crête) exploitable par un fréquencemètre numérique (c'est la moindre des choses...)

C'est aussi de protéger l'AD9951 contre les mauvais traitements susceptibles d'être infligés à la sortie. ;)

C'est un étage différentiel qui en tant que tel atténue les perturbations de mode commun. Comme la sortie du DDS est elle même en mode différentiel, ça tombe bien.

J'ai dans un premier temps testé le principe avec des transistors BC549B, dont la fréquence de transition est de 300MHz, mais dont la capacité collecteur-base importante (qq pF) a pour effet (Miller), dans ce montage émetteur commun, de diminuer la bande passante. Et en effet, cette configuration ne convenait que jusqu'à 5MHz.

Mais avec des BFR93A dont la Ft est = 5GHz, et la capa collecteur-base = 0.45pF, cette version fonctionne jusqu'à 160MHz. Au delà l'analyseur de spectre montre que l'atténuation augmente régulièrement jusqu'à 200MHz (limite haute de la fréquence générée).

Concernant la précision de la fréquence produite, le fréquencemètre numérique affiche, pour une Fo = 10.000000 MHz, une valeur de 10.00192 MHz.

Peut mieux faire, donc. Une petite capa de 15pF entre le pin 8 et AGND réduit cette erreur de moitié.

Ne perdons pas de vue que la fréquence du quartz = 20MHz est x20 par une boucle PLL interne au DDS, pour obtenir 400MHz...

La prochaine amélioration que je vais faire consistera à remplacer le quartz par un oscillateur 100.000 MHz, ou mieux un oscillateur intégré compensé en température (TCXO).

|

17 Version avec un Oscillateur Intégré comme ref. de fréquence (MCO-1510A)

23 oct 2014:

Pour cette nouvelle version j'ai donc remplacé le quartz 20MHz par Oscillateur intégré ( le MCO 1510A, donné pour une précision de +/- 25ppm) de 100MHz. L'entrée OSC/REFCLK (pin 8 de l'AD9851) est maintenant reliée à AGND par un 100nF comme préconisé sur le datasheet (pourquoi une valeur si forte pour de fréquences > 20MHZ ???) et l'entrée OSCREFCLK (pin 9 de l'AD9851)

est attaquée par le signal d'horloge à 100MHz issu du MCO-1510A via un pont diviseur de mise à niveau (5V du MCO-1510A vers 1.8V du DDS) et un condensateur de liaison de 10nF (et pas 100 !)

Quelques modifications ont dû être apportées au programme, en particulier :

- CFR2<7:3>: Reference Clock Multiplier Control Bits = 00100; -> F x 4 (au lieu de x 20)

Voici le schéma obtenu :

|

|

|

|

18 Schéma avec oscillateur intégré MCO-1510A :

Remarques :

- La résistance de 4k7 entre VEE de l'afficheur et le +5V peut-être une 2k2 entre VEE et GND. C'est suivant le type d'afficheur. (en principe il faut utiliser un potentiomètre, mais ça prend une place énorme).

- Le MCO-1510A s'alimente en 5V alors que le MCO-1510B s'alimente en 3V3.

|

|

|

|

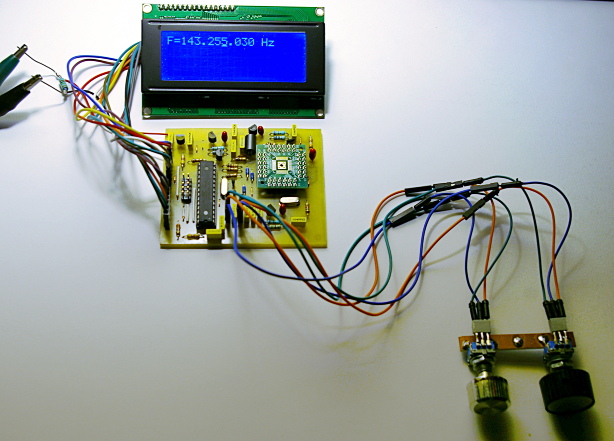

19 Vue d'ensemble de la nouvelle version :

Comme vous pouvez le voir je n'ai pas refait le circuit imprimé, j'ai juste implanté les nouveaux composants plus ou moins "en l'air".

De toute manière si je devais refaire la carte ce serait sans doute en CMS avec ma CNC phototraceuse laser ( qui est en cours de réalisation, voir l'article qui lui est consacré sur ce site)...

|

|

|

|

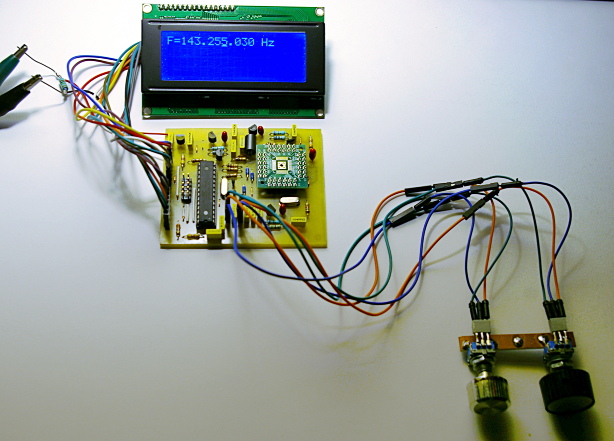

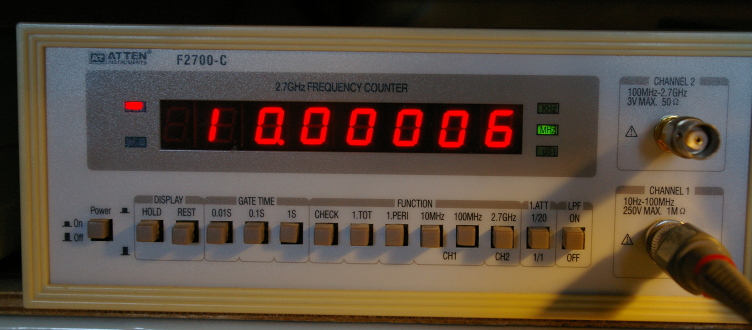

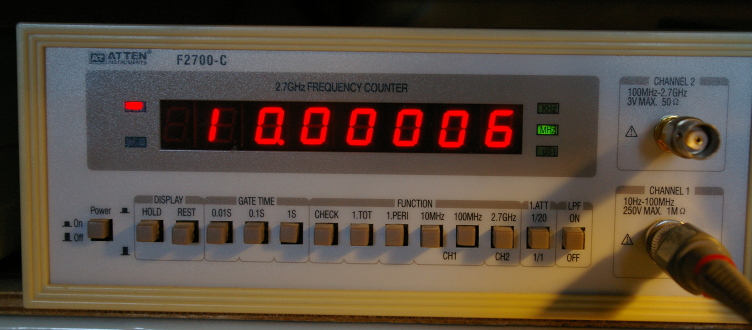

20 Le verdict du fréquencemètre :

|

|

|

|

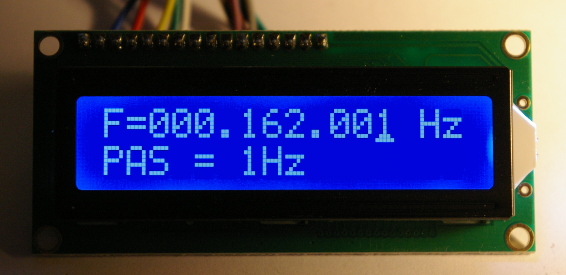

21 Test sur la porteuse de France Inter GO

|

Cela mérite un commentaire:

avec la version à quartz 20MHz, pour une Fo désirée = 10.000000 MHz,

nous obtenions une valeur mesurée de 10.00192 MHz

avec cette version à Oscillateur Intégré 100MHz +/- 25ppm,

nous obtenons une valeur mesurée de 10.00006 MHz ( se situe bien dans la marge d'incertitude de +/- 25ppm )

L'erreur est donc en l’occurrence divisée par 32 !

Toutefois le modèle d'oscillateur intégré que j'ai utilisé (MCO 1510A) n'est pas un TCXO (TC=compensé en température), ces derniers offrant une précision de +/- 0.5ppm à +/- 2ppm, et pas 25ppm !

Reste maintenant à connaître la précision du fréquencemètre qui permettra d'y voir plus clair !

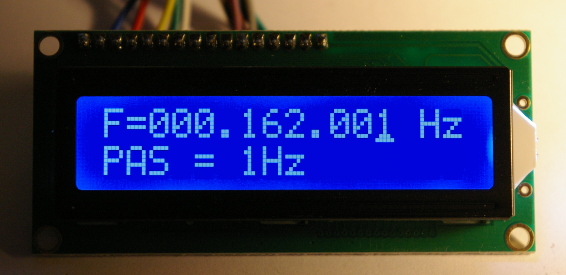

Pour cela une solution simple (dit-on ici et là...) est de prendre comme étalon la fréquence de la porteuse de France Inter GO (162 kHz) qui est pilotée par une horloge atomique au césium avec une précision de +/- 10E-12 (ça devrait le faire), pour étalonner le fréquencemètre.

Dans cette optique, je viens de faire un test rapide : j'ai placé ce générateur à côté d'un recepteur GO calé sur France Inter, voici ce que ça donne à l'oreille :

-sortie 163.000 kHz -> sifflement à 1kHz : c'est "normal".

-sortie 162.001 kHz -> battement audible , période à priori de 1s

-sortie 162.000 kHz -> pas de battement audible

-sortie 161.999 kHz -> battement audible , période à priori de 1s

ça permet de borner l'erreur en fréquence, qui est donc inférieure à

1/162000 = 6x10E-6

ce qui nous donne le même résultat que le fréquencemètre.

( 60Hz / 10 000 060 Hz = 6x10E-6 )

|

Vous remarquerez au passage que l'afficheur a changé de couleur.

Celui-ci a l'avantage d'être rétroéclairé.

Autre précision : Les points ne sont évidemment pas des points décimaux

mais des séparateurs de milliers.

|

|

|

22 Comment obtenir une grande précision de la fréquence ?

Oui, mais pourquoi cela ne nous donne-t-il pas un bornage avec une précision de 10E-12 qui est celle de France Inter GO ?

Tout simplement parce que pour atteindre cette précision il faut faire une mesure pendant 1 million de secondes, c'est à dire 10 jours, ou détecter une erreur de phase de 1/1000 de la période au terme d'une mesure de 1000s (17 minutes environ, ce qui est déjà plus raisonnable, quoi que 1/1000 de la période c'est 6ns !!! ).

Très bien, mais ne pourrait-on pas obtenir plus simplement et rapidement une mesure précise ?

Oui, c'est possible, en prenant comme étalon de fréquence une station de radio WWV en ondes courtes à 10MHz, 15, ou 20MHz par exemple.(Je lis sur Wikipédia : Les fréquences porteuses peuvent être reçues sur la terre entière selon la propagation et permettent de caler avec précision les récepteurs de trafic, en particulier la fréquence 15 MHz en Europe).

25 oct 2014:

Très bien, mais la réception des émetteurs lointains en ondes courtes est connue pour être aléatoire, et sujette au "fading" et à toutes sortes d'interférences... Pas d'autres solutions ?

Si bien sûr !

- La plus simple consiste à utiliser un OCXO (oscillateur thermostaté ) à priori 100 fois plus précis (10E-8) qu'un TCXO. Mais ça consomme bien plus et il est bon de le recalibrer périodiquement...

- Se baser sur la fréquence de balayage H reconstituée par les récepteur TNT qui sont censés être synchrones et précis... à vérifier.

- Acquérir un générateur 10MHz à horloge atomique au rubidium (ne riez pas, en en trouve à partir de 200€, moi je pensais 10 x plus cher !)

- Peut-être une excellente solution, utiliser un récepteur GPS. Ils délivrent un signal 10MHz avec une précision de 10E-12 (si calés sur les satellites) !! ouah ! Cherchez "NEO-7M GPS Module" sur Internet"

ATTENTION : seules les versions NEO-6T et NEO-7...) permettent de configurer le pin TIME PULSE pour fournir un signal de 10MHz. La version la plus courante, la NEO-6M ne permet pas de sortir autre chose que 1Hz !

|

|

|

|

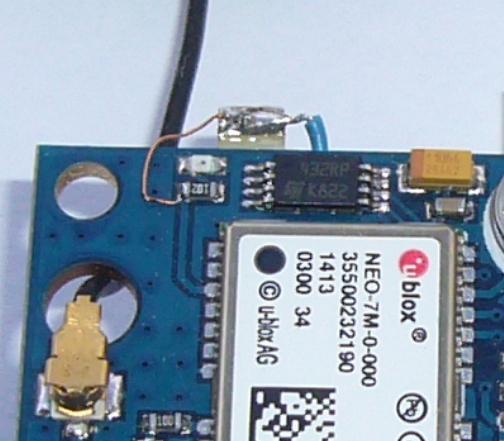

23 Le module GPS - NEO-7M

26 oct 2014:

J'ai commandé un module GPS - NEO-7M

|

|

|

|

24 Remarque :

|

Quoi qu'il en soit de la précision de l'oscillateur de référence utilisé, on pourra toujours compenser son inexactitude absolue puisque le "tuning word" est un mot de 32 bits, ce qui permet d'ajuster la fréquence de sortie avec une acuité de 1/2³² soit 0,2 x 10E-9 ce qui est très "honorable". Toutefois cet ajustement ne règle pas un éventuel problème de dérive de la fréquence de référence dans le temps. D'où l’intérêt de la possibilité de contrôler la fréquence au moyen d'un récepteur GPS. Je vais donc persister dans cette voie.

|

|

|

|

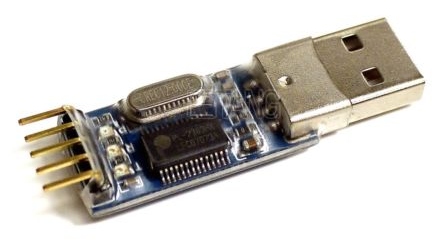

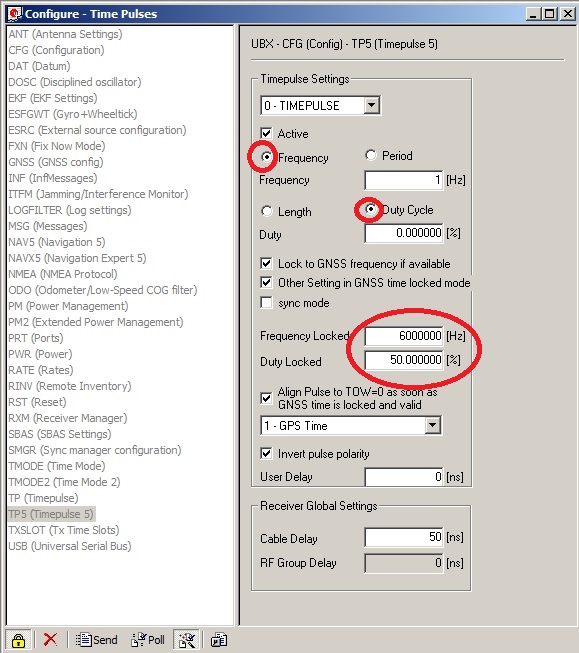

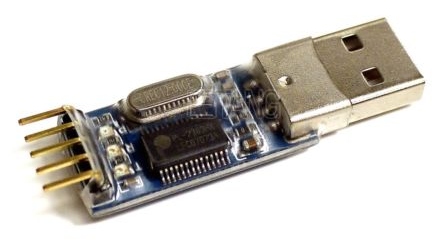

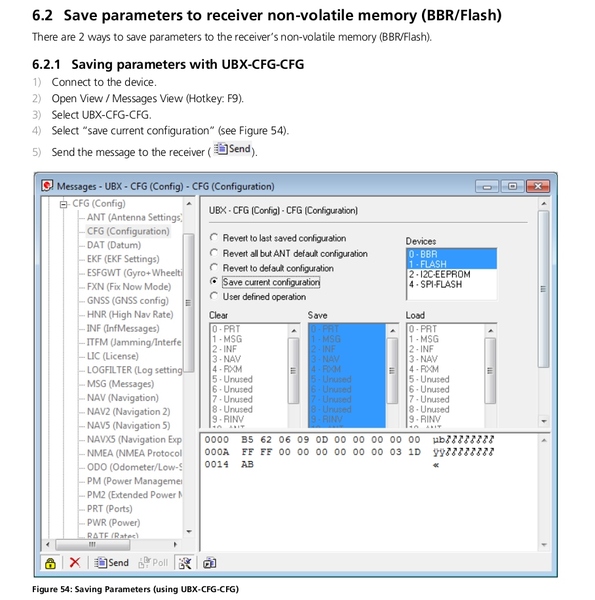

25 Configuration du module GPS - NEO-7M

05 mai 2015:

Je reprends cette étude après l'avoir mise sur la touche pendant six mois durant lesquels je me suis consacré à la fabrication de ma machine photo-flasheuse de circuits imprimés par diode laser 405nm, dont vous trouverez la description sur ce site.

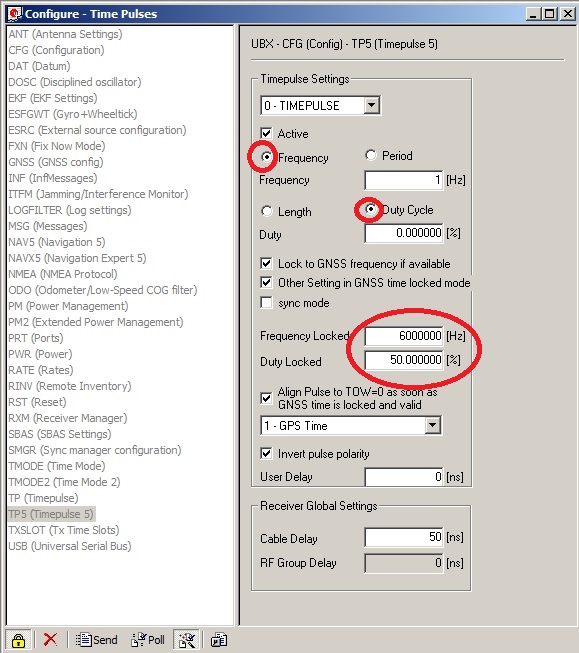

Depuis j'ai bien sûr reçu le module GPS - NEO-7M et je dois dire de suite qu'il tient ses promesses : Le signal fourni est facilement exploitable pour étalonner un fréquencemètre. Il faut toutefois commencer par configurer ce module afin qu'il produise un signal de 8.000000 MHz, car par défaut il sort... 1Hz qui fait clignoter une led !

La configuration se fait par une simple liaison au PC par l'intermédiaire d'un adaptateur USB/TTL.

La marche à suivre est très bien expliquée sur cette page :

|

|

|

La page est écrite en russe ce qui ne pose aucun problème (un petit coup de G...l traducteur et la transcription s'affiche dans un français presque parfait ce qui est loin d'être le cas pour la traduction des sites en anglais !! Le russe serait-il plus proche du français que l'anglais ? Il me semble que Cavanna nous avait dit ça en effet).

Le datasheet du récepteur NEO-7 laisse entrevoir que sa programmation n'est pas simple. Heureusement le fabriquant fourni un petit programme de configuration très complet (mais très déroutant) "u-center". Petit problème ce programme n'est disponible que pour Window$ ou Androïd. Petite solution : Utiliser wine sous Linux. Et ça marche. (après avoir créé un lien symbolique de com1 vers ttyUSB0 dans le dossier de config de wine par la commande suivante :

ln -s /dev/ttyUSB0 ~/.wine/dosdevices/com1

puis il faut donner les permissions :

cd ~/.wine/dosdevices/com1

sudo chmod 777 ./com1

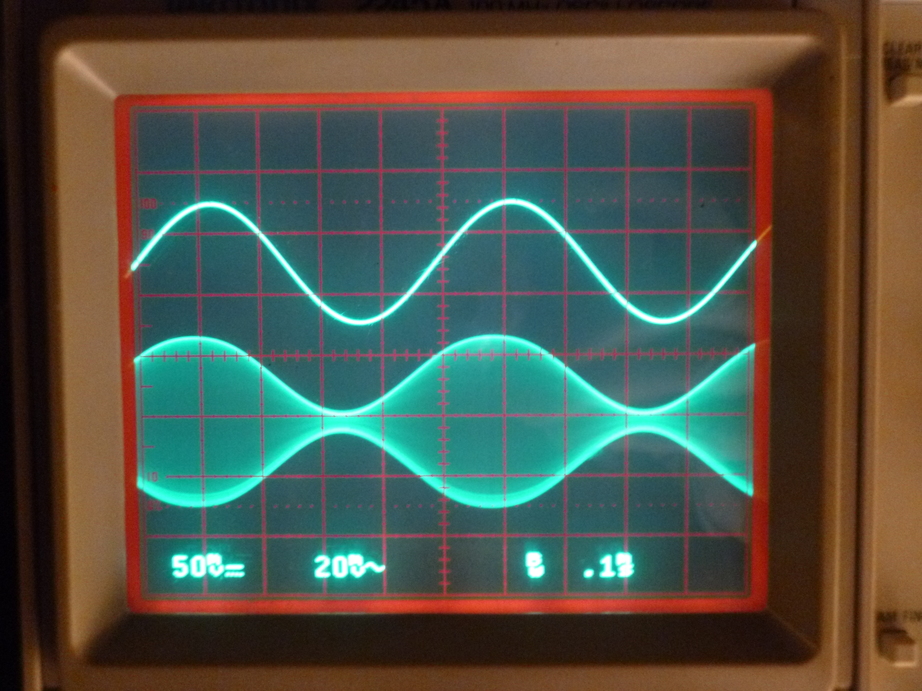

Le signal obtenu est extrêmement précis en fréquence mais très bruité en phase ce qui le rend impropre à constituer directement une base de temps, mais permet une comparaison de fréquences facile à l'oscilloscope par figure de Lissajous. Il est d'ailleurs impressionnant de voir une figure de Lissajous stable à cette fréquence !

|

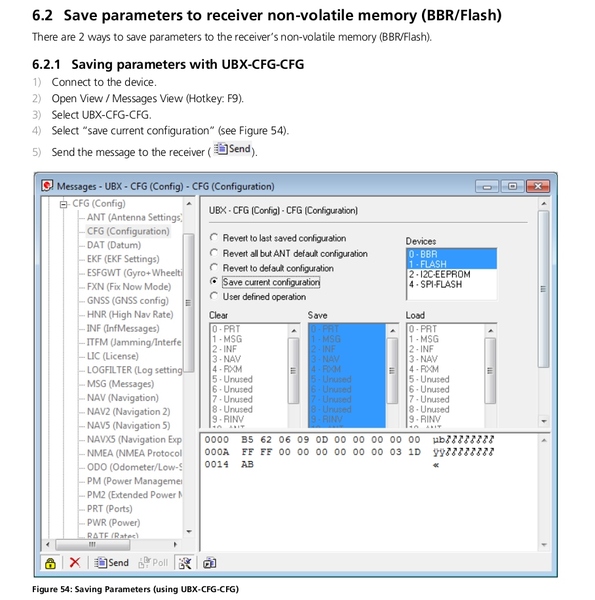

26 Captures d'écran du logiciel

Ces deux images vous montrent la marche à suivre. Ce logiciel est une usine à gaz. Sans lire la doc je pense qu'il est très improbable de pouvoir l'utiliser.

|

|

|

|

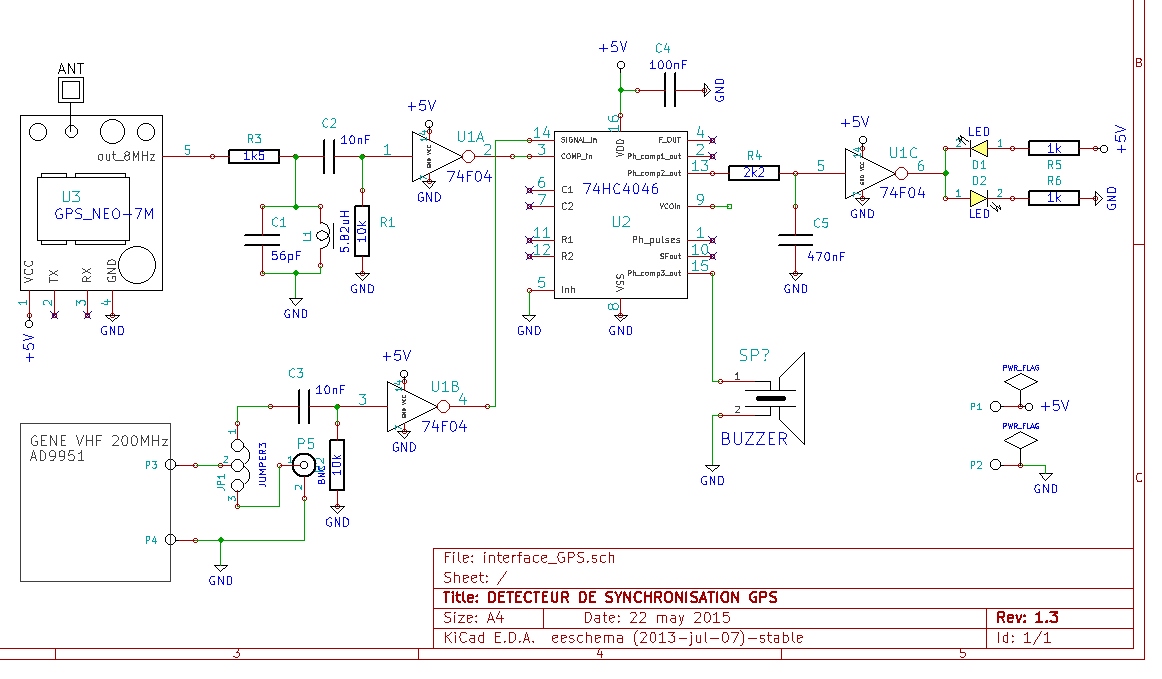

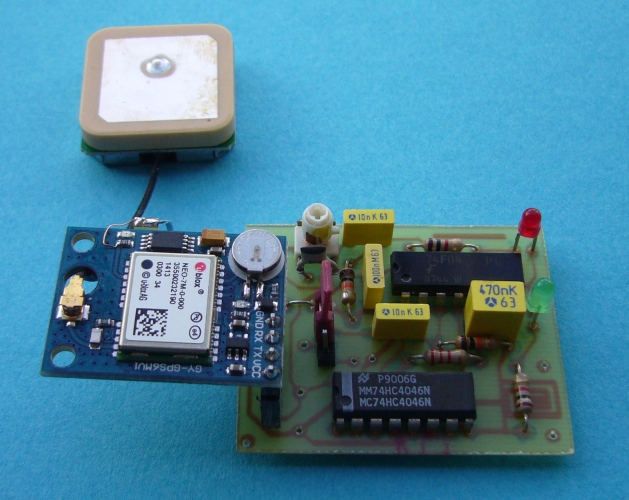

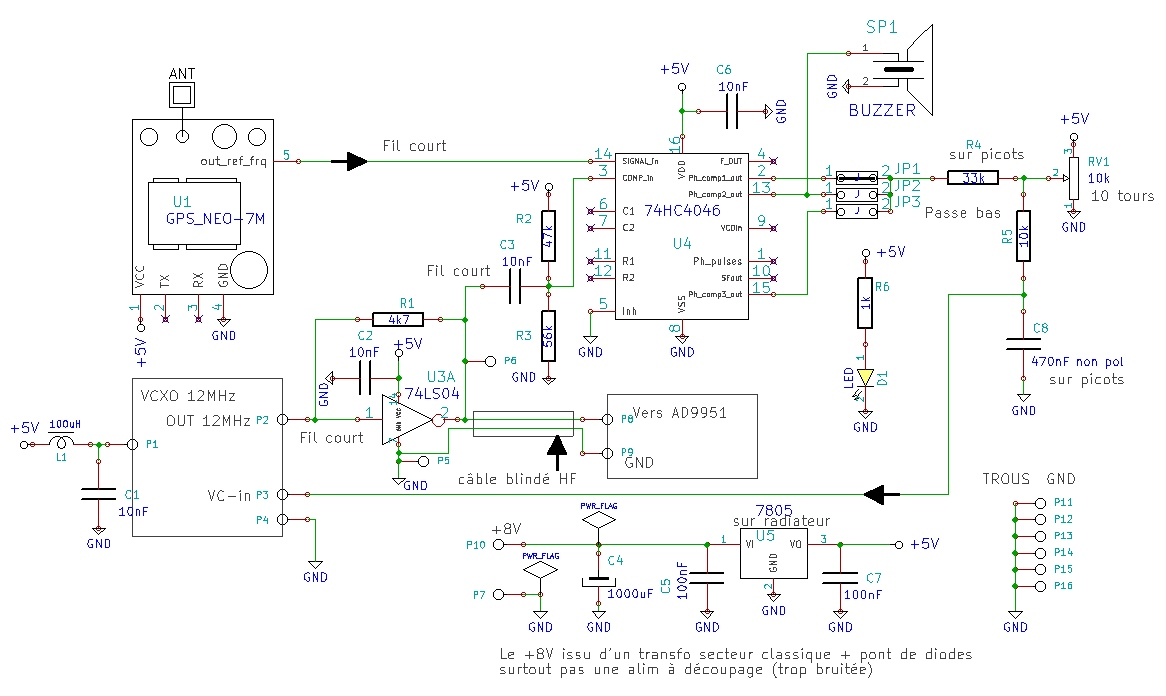

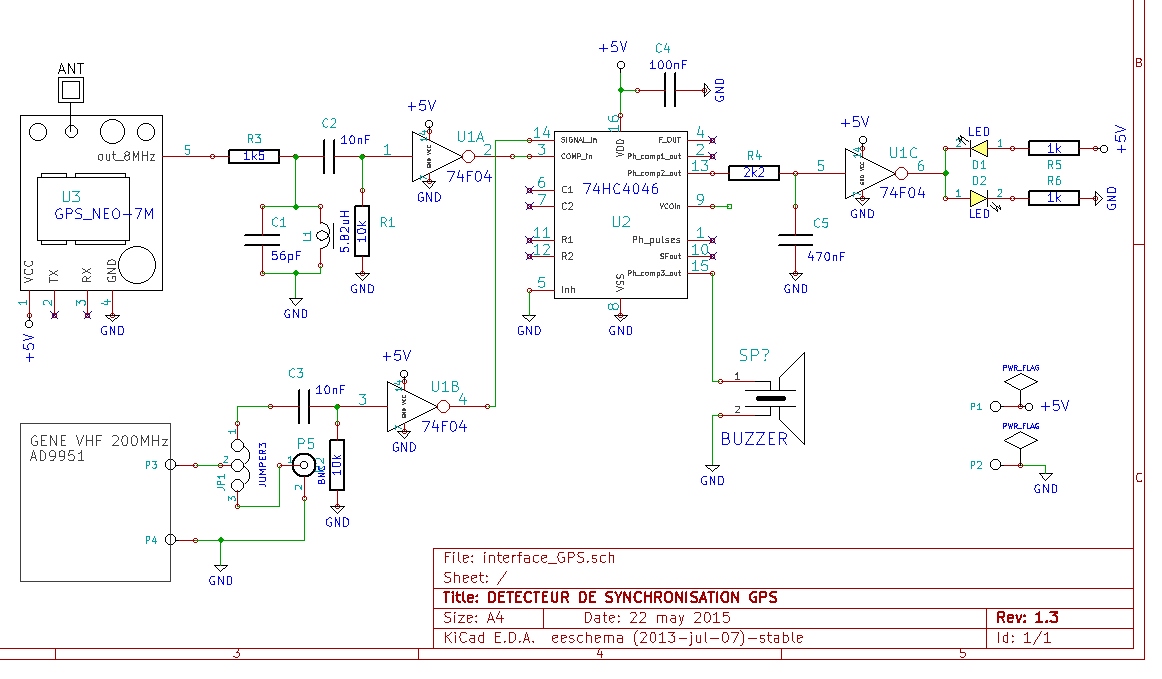

27 Détecteur de synchronisation

Nous avons donc notre module récepteur GPS NEO-7M correctement paramétré. Ne pourrait-on pas se passer d'un oscilloscope pour étalonner le fréquencemètre ? Si, grâce à ce ce montage utilisant un circuit PLL en HC-MOS (rapide donc, pas un simple CD4046 !) 74HC4046, dont je n'utilise que le détecteur de phase (il en comporte 3 différents en plus d'un VCO). La sortie de ce comparateur de phase pilote deux LEDs, une rouge et une verte, ce qui permet de détecter visuellement et facilement la synchronisation entre le signal 8.000000MHz issu du récepteur GPS et celui produit par le géné VHF. (Les leds clignotent de plus en plus lentement lorsqu'on se rapproche de la synchronisation, jusqu'à devenir fixes. On voit alors qu'un simple souffle d'air frais sur l'oscillateur à quartz intégré du géné suffit à faire dériver la fréquence (certes d'une valeurs très faible de quelques ppm... mais pas nulle)).

Pour éviter de déformer le précieux signal de sortie du géné, un jumper à deux positions connecte cette sortie soit à la prise BNC de l'appareil soit au détecteur de synchronisation, mais pas les deux à la fois.

|

|

|

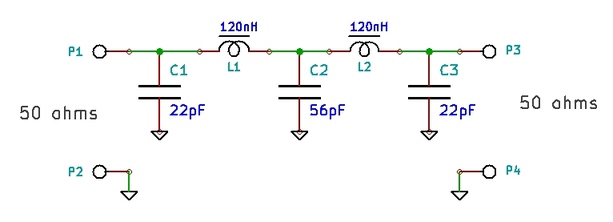

Le petit "circuit bouchon" LC câblé sur la sortie 8MHz du récepteur GPS sert à diminuer le "jitter" (bruit de phase) très important dont je vous ai parlé précédemment. Il importe de caler précisément la fréquence de résonance de ce circuit sur 8.000MHz (rechercher l'amplitude maximale à l'oscilloscope, en tournant le petit noyau de la self).

|

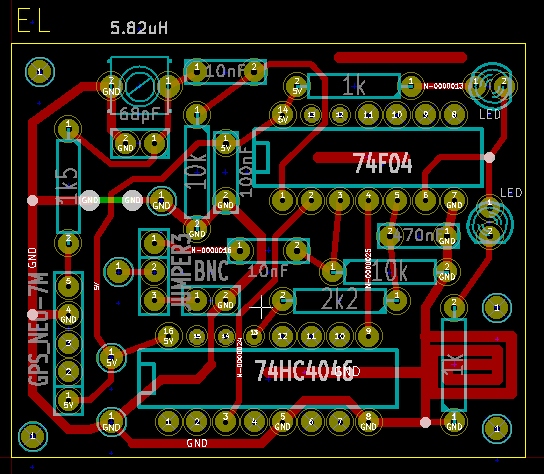

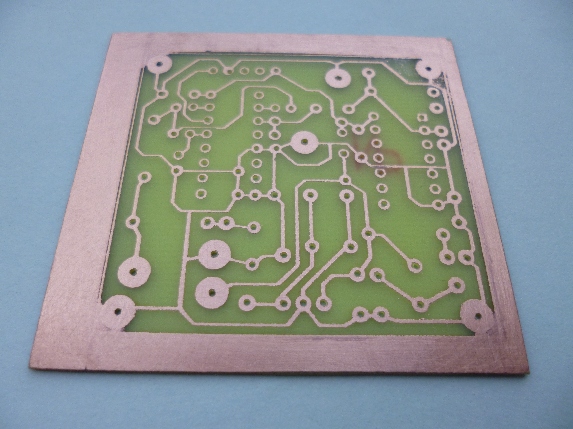

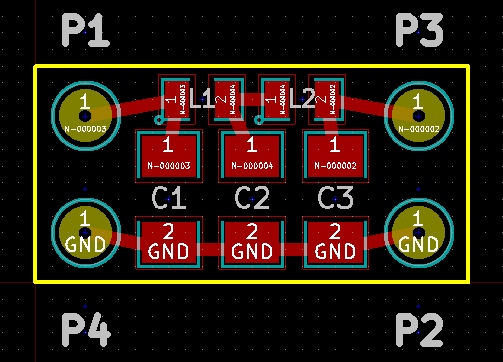

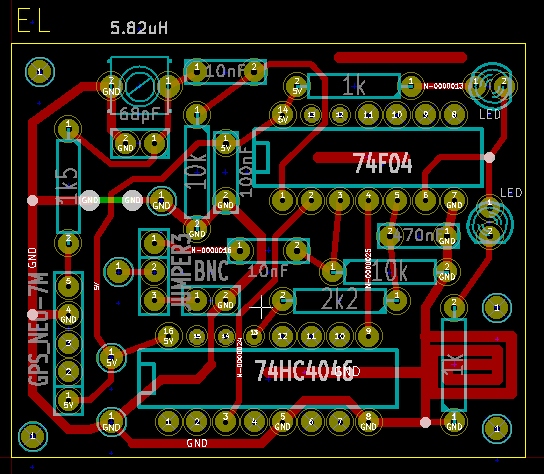

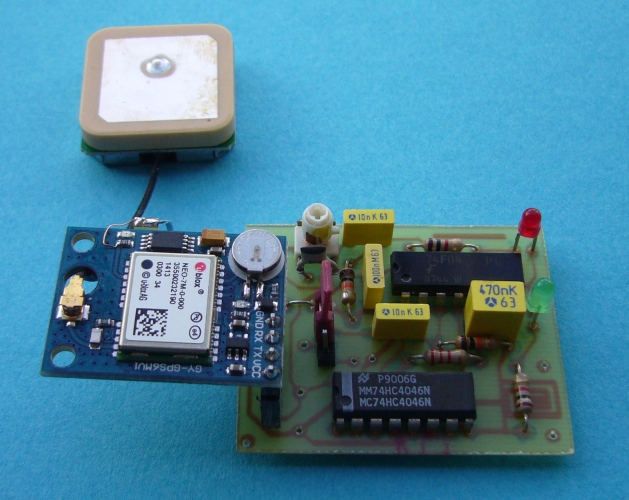

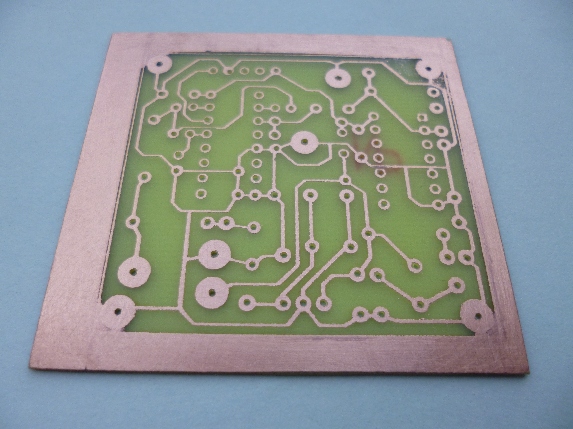

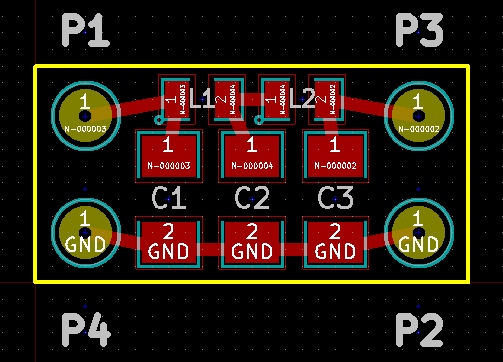

28 Le circuit imprimé du détecteur de synchronisation :

|

16 mai 2015:

Ce circuit imprimé est en cours de réalisation.

Il sera flashé avec ma toute nouvelle machine laser !

Le petit module GPS NEO-7M viendra se connecter directement sur le connecteur vertical visible en bas à gauche. Sur la partie droite sont disposées les deux LEDs de détection de glissement de phase.

|

|

|

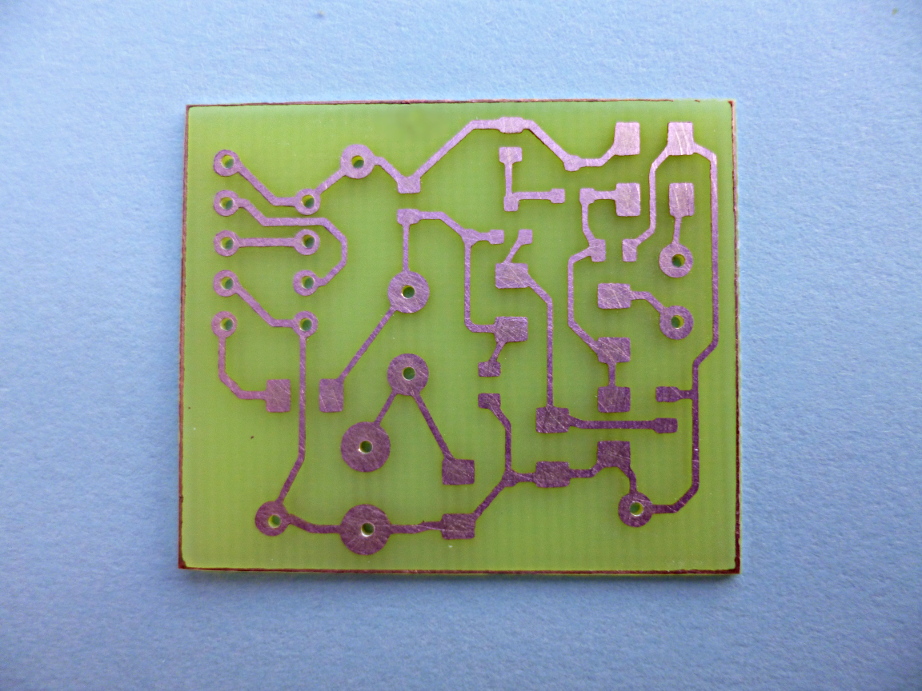

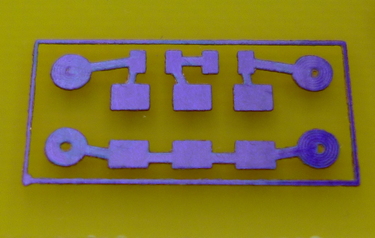

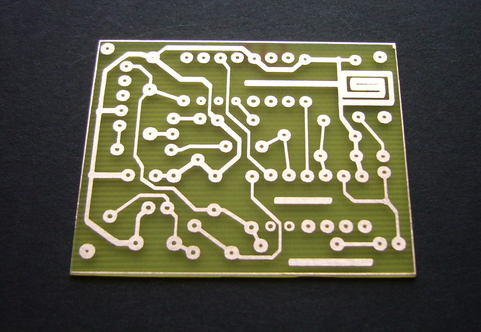

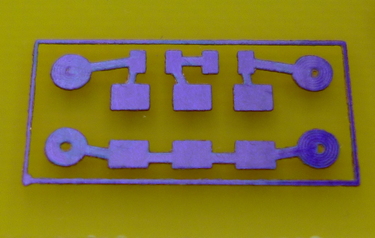

29 Circuit imprimé flashé

|

20 mai 2015:

Voici donc le circuit imprimé prêt pour le perçage et soudage des composants. Le flashage a été effectué par ma flasheuse laser 405nm, en image miroir puisqu'il s'agit du coté cuivre alors que le dessin du circuit sous le logiciel libre Kicad se fait côté éléments.

J'ai expérimenté des "plans de masse" sous forme de pistes de largeur 1mm. Le résultat est précis en ce sens que les espaces entre ces pistes ont été reproduits (ce dont je me serais bien passé !). Il suffira de resserrer ces "pistes de masse" à l'avenir. Dans le cas présent ces pistes ne servent qu'à... économiser le perchlorure de fer lors de la gravure tout en accélérant ce temps de gravure.

|

|

|

30 Proto terminé

|

|

|

Et ça marche ? Non, puisque en l'électronique tout prototype non testé est réputé NE PAS fonctionner (alors que tout proptotype testé tombera en panne de préférence lors d'une démonstration). Sauf bien sûr dans le domaine spatial où en envoie à des milliards de km des trucs non testés parce qu'on n'a pas d'astéroïde dans le labo...

Dernière minute : Il y avait bien une erreur dans la saisie du schéma !!! (confusion entres les pins 9 et 14 du 74HC4046)

J'ai corrigé le schéma. Je vais faire la correction sur le circuit imprimé et je continuerai à tester.

|

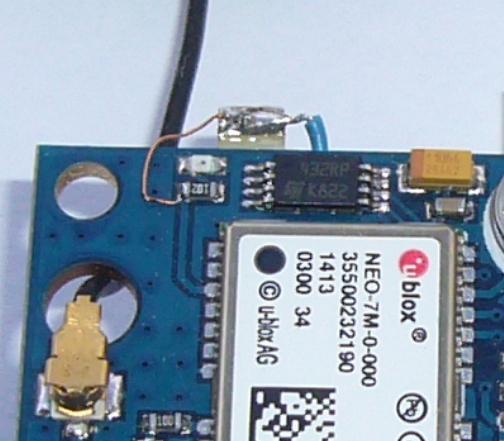

31 Un petit détail :

|

Le signal 8MHz généré par le module GPS fait clignoter (il est livré paramétré sur 1Hz) une LED cms, mais n'est pas câblé d'origine sur un pin de sortie. Cela oblige à souder un fil sur la piste qui alimente (par une 1K) cette LED. Vu la taille des composants cms, le fil (émaillé) doit être fin comme un cheveu (15/100mm). J'ai ajouté un point de soudure via un petit rectangle de circuit imprimé (en 8/10mm) soudé au plan de masse sous la carte, d'où part un fil (très) souple un peu plus gros (mais en fait très fin lui aussi).

|

|

22 mai 2015:

J'ai rajouté un petit buzzer piezo sur une des trois sorties du comparateur de phase, ce qui augmente l'ergonomie du synchroniseur : Pour un décalage de fréquence de plusieurs dizaines (voire centaines) de Hz l’œil ne permet plus de suivre les clignotements des LED, mais l'oreille prend alors tout naturellement le relais. Tout ça dans le but de ne pas devoir utiliser l'oscilloscope. Et comme le signal en sortie du comparateur n'est pas très "propre" (dû tout simplement au fait que le signal 8.000000MHz en sortie du GPS est entaché d'un très important bruit de phase comme nous l'avons vu plus haut), l'oreille continue de percevoir quelque chose même pour des fréquences de l'ordre du Hz (une sorte de respiration issue tout droit d'un film de science fiction, il doit y avoir une attaque d'Alien sur un des satellites du GPS).

|

32 TCXO en commande...

23 mai 2015:

Je viens de commander aux USA un vrai TCXO 20MHz (oscillateur intégré compensé en température) pour environ 11€. Voici le lien vers cet article :

En principe la fréquence ne devrait plus dériver lorsqu'on souffle dessus ! Nous verrons bien.

|

|

|

|

33 Passage à une base de temps TCXO

|

13 août 2015:

Cela fait bien deux mois que j'ai reçu le TCXO, mais faute de temps il est resté dans le tiroir. Aujourd'hui je l'ai essayé et comparé au signal GPS ( précis à 10E-12 je le rappelle) et je peux déjà dire qu'en effet la fréquence ne bronche plus lorsqu'on souffle dessus ! Je suis en train de l'incorporer au générateur et de modifier sa programmation en conséquence.

|

|

|

|

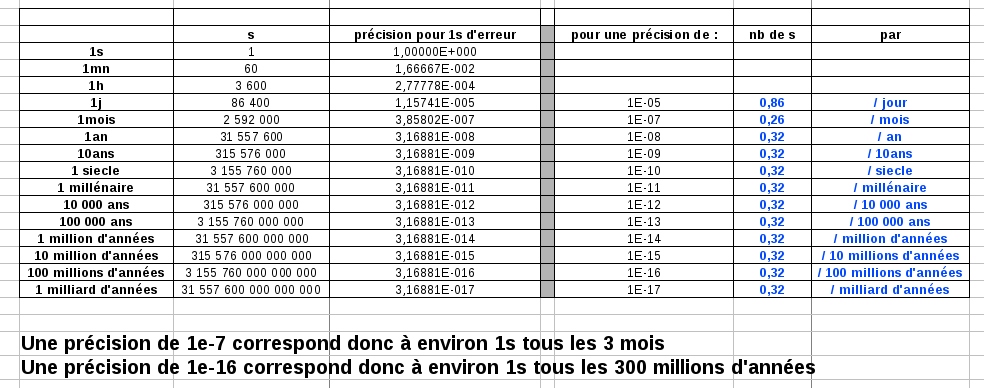

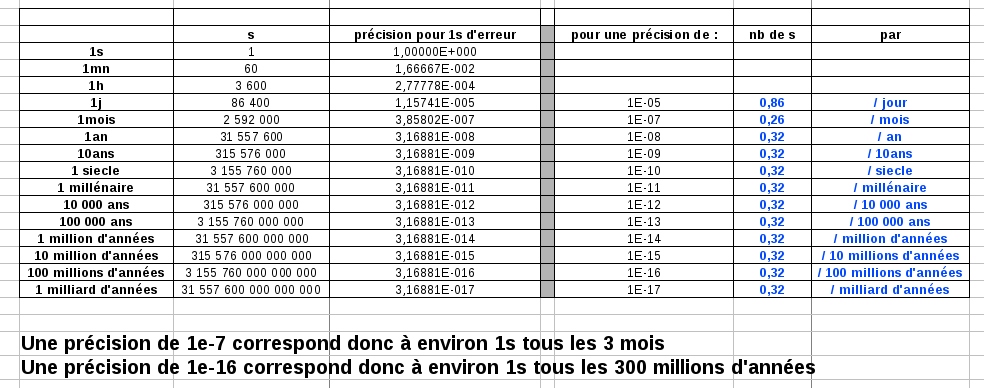

34 Tableau de précision temporelle

j'ai calculé ce tableau qui donne les écarts de temps correspondants à une précision donnée. Je reconnais que certains résultats m'ont étonnés moi-même. La précision du GPS en particulier est remarquable (0,3s en 10 000 ans... waouh !)

|

|

|

|

35 Cogitations en direct :

15 août 2015:

Je suis en train d"expérimenter autour du bruit de phase du signal 10MHz (par exemple, c'est programmable on l'a vu) reconstitué à la sortie du module récepteur GPS - NEO-7M.

Ce bruit de phase est épouvantable ! Le signal apparaît propre et dépourvu de tout bruit de phase lorsqu'on le visualise seul à l'oscilloscope synchronisé par lui même. Mais il en va tout autrement si l'on synchronise l'ocsillo sur un autre signal 10MHz issu d'un générateur indépendant précis et stable. Et le résultat est le même quel que soit le générateur utilisé comme référence de phase. Le signal issu du GPS est entaché d'une modulation de phase qui atteint 30% de la durée de la période pour cette fréquence de 10MHz. Autant dire qu'il n'est pas concevable de l'utiliser tel quel pour piloter la base de temps d'un générateur (comme celui que nous décrivons ici par exemple).

Il y a la solution qui consiste à piloter une PLL avec une grande constante de temps dans la boucle d'asservissement. Mais devant les difficultés rencontrées je creusé un peu plus et je me suis aperçu que les fluctuations de phases se font d'un manière qui semble aléatoire, suivant toutes sortes de fréquences dont les plus basses sont vraiment très... basses.

J'ai essayé de calmer le bruit de phase en faisant passer le signal par un filtre à quartz 8.000MHz. Le signal qui sort est tout joli bien sinusoïdal, mais de phase tout autant fluctuante !

Je sais que le bruit de phase à plusieurs causes :

- L'effet Doppler dû au mouvement des satellites qui ne sont pas géostationnaires.

- Le fait qu'on reçoive les signaux de plusieurs satellites.

- Les fluctuations de la célérité des ondes électromagnétique lorsqu'elles traversent l’ionosphère (elle est alors < c) qui est... ionisée et fluctuante.

- Un brouillage volontaire par l'Oncle Sam pour dégrader la précisions de la position sur les appareils civils.

Mais j'ai aussi entendu dire que sur des durées plus longues (la seconde par exemple) le nombre de périodes reçues est exact.

Je me suis donc demandé à partir de quelle fréquence on peut considérer que le rattrapage de périodes masque le bruit de phase. j'ai donc programmé le module NEO-7M afin qu'il génère diverses fréquences, de plus en plus basses, voici ce que je constate :

- 10MHz -> bruit de phase épouvantable

- 1MHz -> bruit important

- 100 kHz -> bruit moyen

- 10kHz -> bruit très faible, à peine perceptible à l'oscillo

Pour cette dernière valeur (10kHz) j'ai mesuré une fluctuation de +/- 0.1us autour de la valeur moyenne de la durée de la période (100us), soit 0,1%.

Je pense que dans ce cas on peut utiliser une PLL comme le 4046 vu plus haut afin d'obtenir un signal parfaitement propre et d'une précision en fréquence excellente.

Oui mais obtenir en fin de compte un signal de 200MHz à partir d'une base de temps à 10kHz sans rajouter... de bruit de phase, me semble bien présomptueux, voire impossible !

Voyons dans le tiroir s'il n'y a pas un morceau de rubidium qui traîne.

|

|

|

|

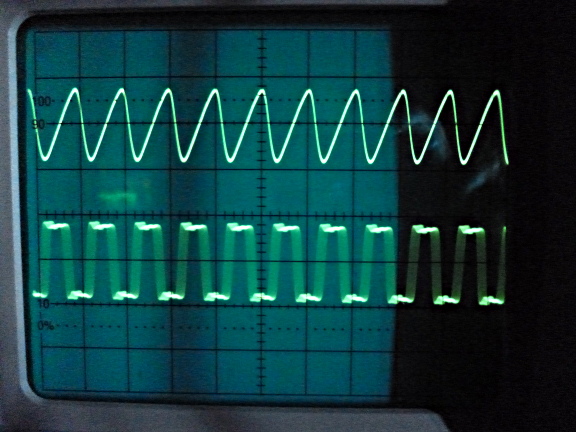

36 Une solution sérieuse en vue

|

|

|

18 août 2014:

Nous avons vu que l'utilisation d'un quartz comme filtre ne supprimait pas le bruit de phase. Une PLL (boucle à verrouillage de phase non plus). Je me suis aperçu que cela est dû non pas à un suivi de la modulation de phase par le biais de l'asservissement, ce qui me paraissait inexplicable vu le filtre passe bas à longue période inséré dans ladite boucle, mais... par un couplage HF entre le signal entrant (issu du GPS) et le VCO de la PLL, couplage très "lâche" certes, j'avais quand même découplé les alims, couplage sans doute électromagnétique (à 8MHz il faut en fait tout blinder, ce n'est plus de la BF), et couplage d'autant plus efficace que le VCO de la PLL utilisée (un HCT40106) et constitué par un simple circuit "à relaxation" RC, dont le Q équivalent est au raz des pâquerettes.

J'ai alors pensé à câbler une PLL maison avec comme VCO un circuit oscillant LC, avec un Q de plusieurs centaines ou plus. Mais s'est vite imposé la conclusion que la stabilité en fréquence de ce genre d'oscillateur est vraiment minime, sans compter les signaux parasites qui pourraient être reçus. A tel point que la mise au point s'est avérée trop délicate.

Le TCXO offre quant à lui une excellente précision et stabilité de la fréquence, il est ajustable, mais il a un défaut rédhibitoire :

L'ajustage ultra précis de la fréquence est mécanique, en tournant un microscopique condensateur ajustable, dont la vis de réglage n'est pas faite pour être utilisée à répétition : fragile, fente pas assez profonde, pratiquement HS après une journée de manip. Il existe des TCXO ajustables par tension, mais on les trouve très difficilement, c'est la galère.

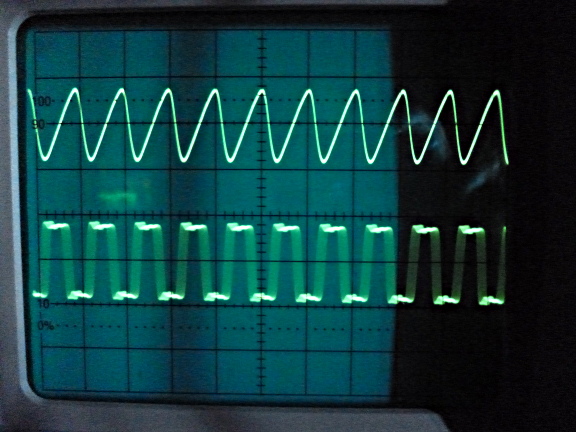

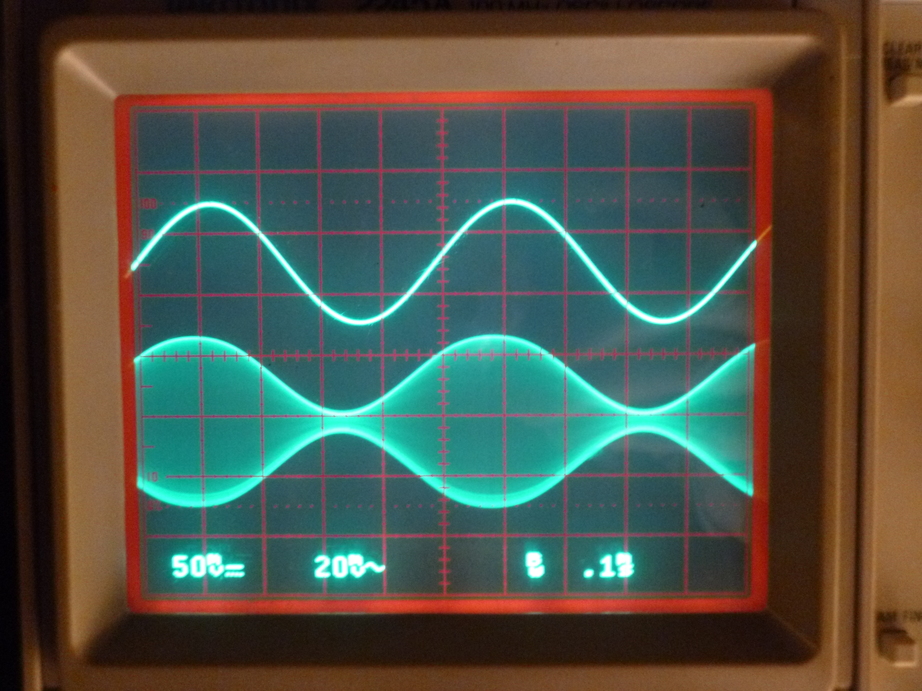

J'ai eu alors l'idée de réaliser une PLL maison dont le VCO serait un simple quartz dans un oscillateur Colpitts (un seul transistor et qq condos) dont je ferais (très) légèrement varier la fréquence par une self ou un condensateur en série. L'idéal est d'utiliser un quartz de fréquence nominale 10MHz (ou 20) mais de fréquence réelle légèrement inférieure (9.999MHz environ) dont on augmente la fréquence par un condensateur, une diode varicap en occurrence située dans la boucle d'asservissement. J'ai donc expérimenté cette solution, et alors surprise, pas besoin de varicap ni d'asservissement, un simple couplage (très très très très très très) lâche suffit pour que cet oscillateur se synchronise sur la fréquence du signal 10MHz issu du module GPS. Et sans bruit de phase s'il vous plaît !!!! Voyez plutôt la photo, sachant que l'oscillo n'est pas synchronisé sur l'un des deux signaux affichés, mais sur un troisième signal de référence, ce qui prouve que le bruit de phase visible affecte bien le signal GPS et non celui généré par l'oscillateur à quartz.

Une fois tout cela incorporé au géné à AD9951, nous obtiendrons l'équivalent d'une référence au rubidium.

|

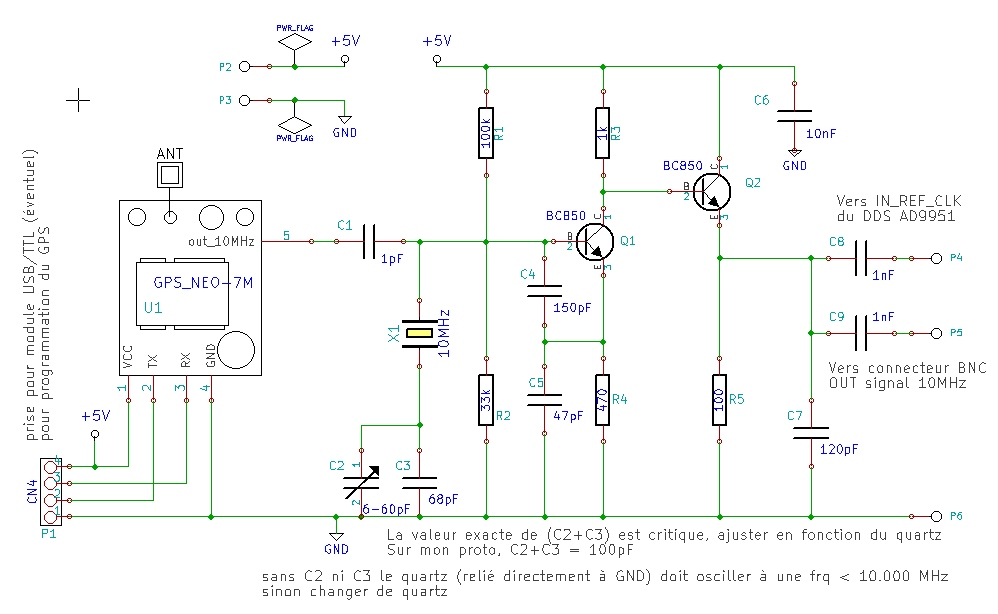

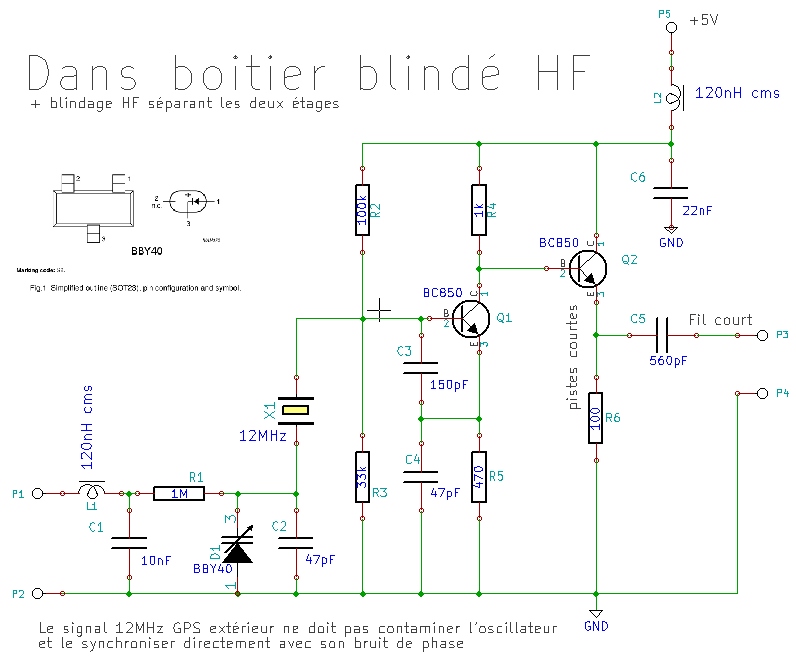

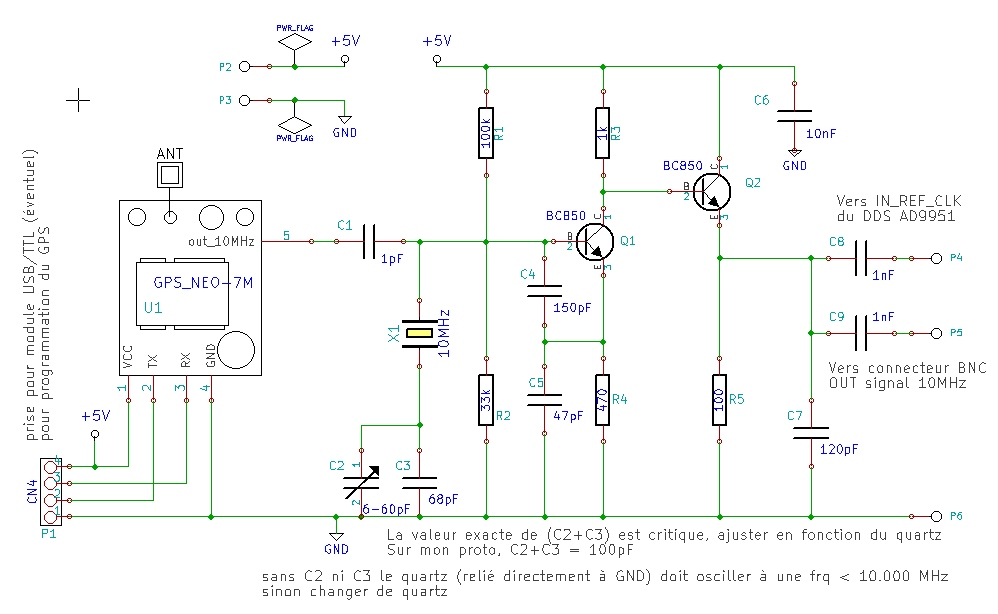

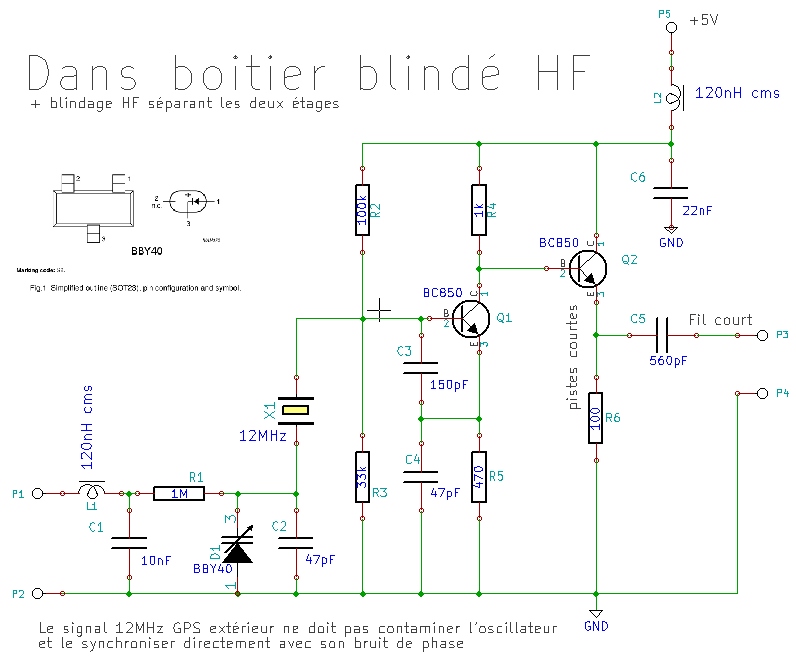

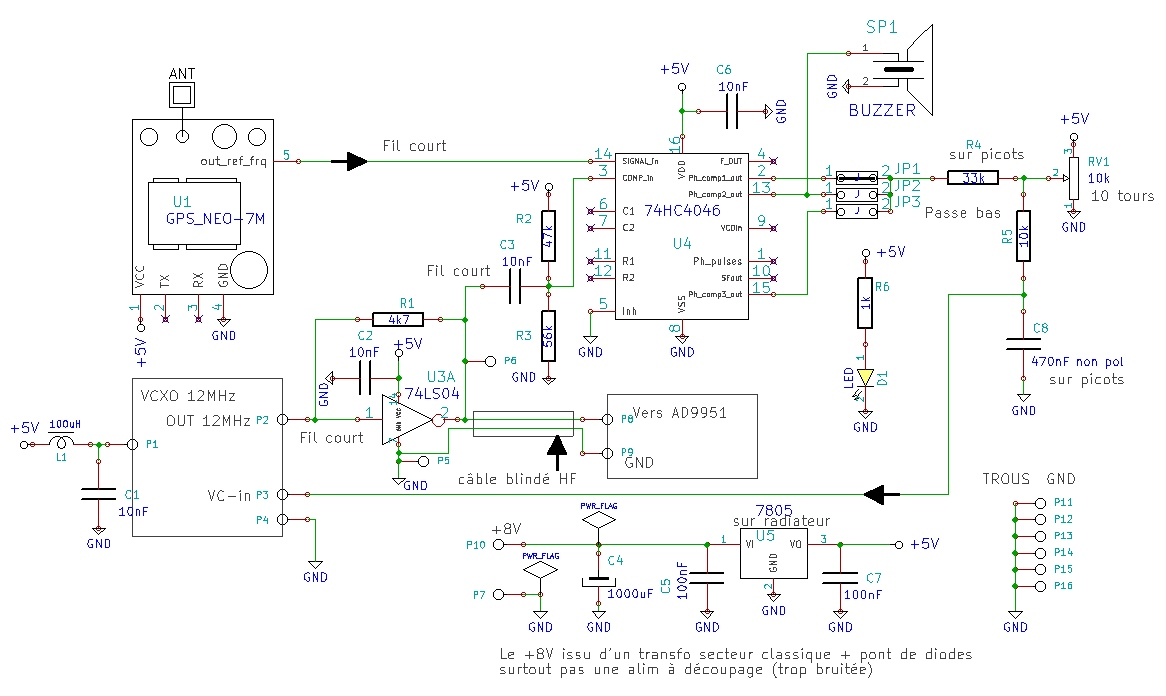

37 Base de temps GPS

Il est beau le titre de ce paragraphe, n'est-ce pas ? Et oui, ça fonctionne ! J'ai ajouté un étage adaptateur d'impédance pour attaquer le DDS AD9951, et ça fonctionne en continu, sans problème sur le plan électronique. Voici donc le schéma de cette base de temps.

Q1, C3 et C4 et le quartz constituent un oscillateur Colpitts classique. Le condensateur en série a pour effet de rehausser très très légèrement la fréquence d'oscillation du quartz pour l'amener aussi proche que possible d'exactement 10.000000000 MHz pour que le verrouillage sur le signal 10MHz du GPS se fasse (il faut donc choisir un quartz oscillant à une fréquence légèrement inférieure à 10.000MHz, mais marqué 10MHz sur le boitier, n'allez pas essayer un quartz de 9,5 MHz !!!!). Le couplage très lâche entre le GPS et l'oscillateur Colpitts est obtenu par un condensateur de 1pF.

Remarque : cet appareil était au départ en mesure de fournir un signal de sortie à 200MHz tant qu'il utilisait comme base de temps un quartz à 100MHz ou 20MHz ou un TCXO 20MHz. Le passage à une base de temps GPS ne permet qu'une référence à 10MHz, et vu que la PLL interne au 9951 ne permet qu'une multiplication par 20, cela nous donne une référence interne à 200MHz. Oui mais le signal de sortie ne doit pas dépasser la moitié de la valeur de cette référence interne, donc 100MHz. La limitation (à 10MHz en entrée) n'est sans doute pas incontournable mais je préfère m'en tenir à ça tout en bénéficiant de la précision du GPS.

|

|

|

|

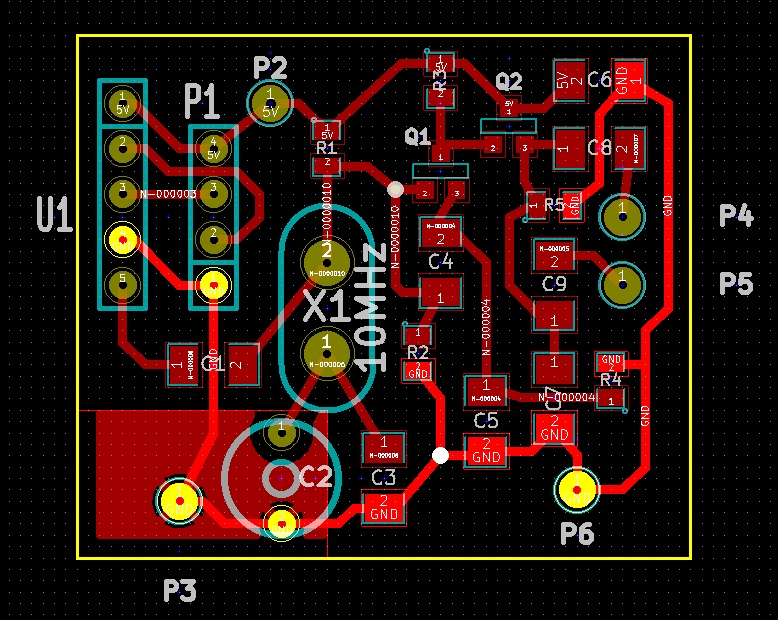

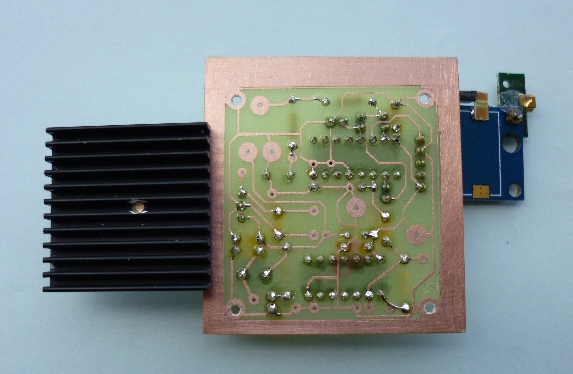

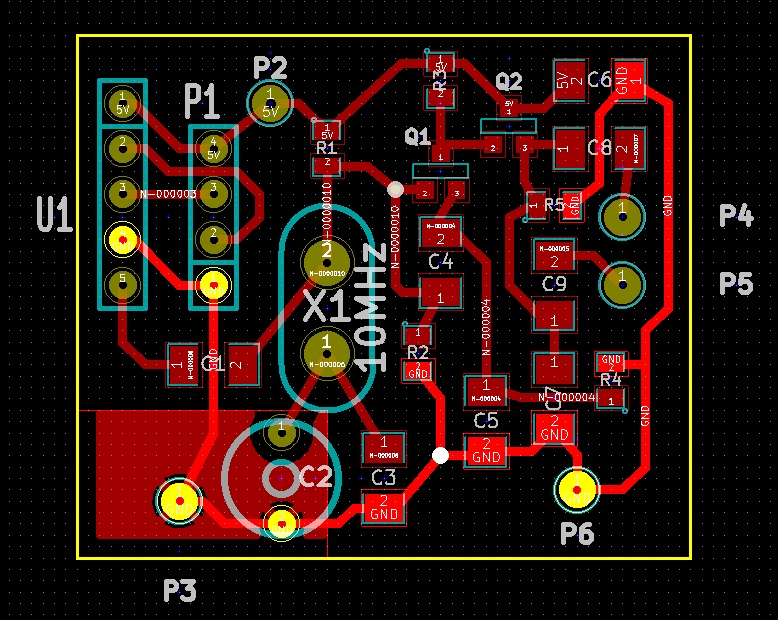

38 Circuit imprimé de la base de temps

|

22 août 2015:

Le circuit imprimé est en cours d'étude

|

|

|

|

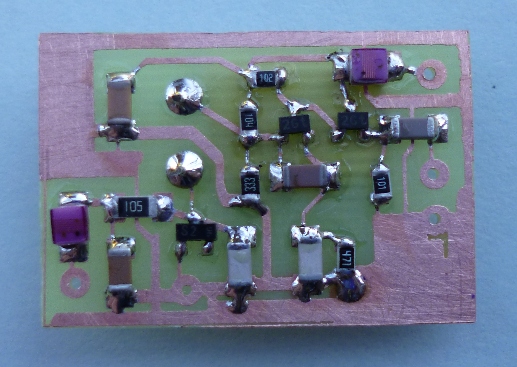

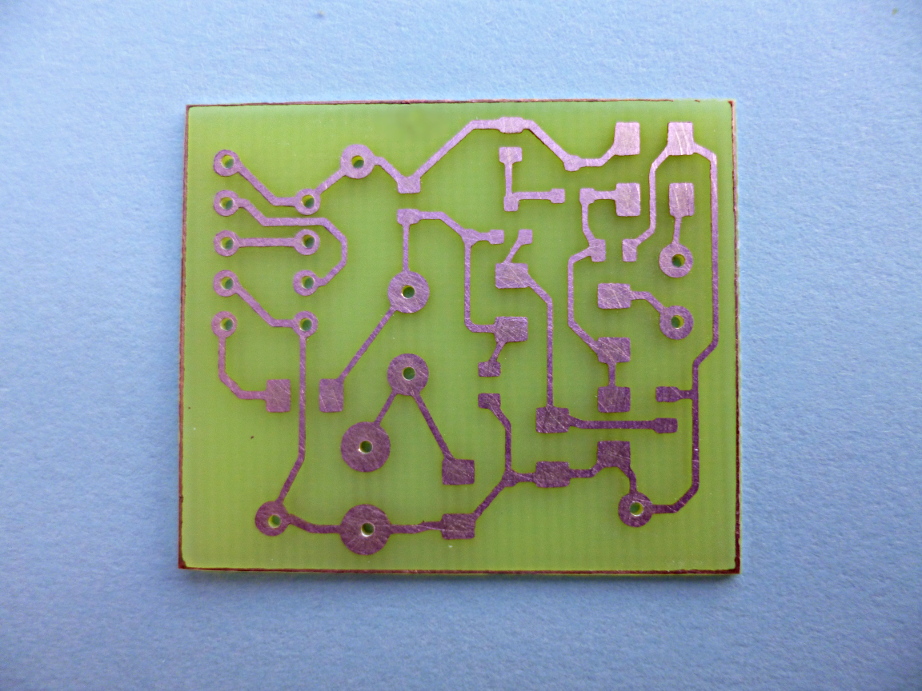

39 circuit gravé :

24 août 2015:

J'ai flashé le circuit avec ma machine laser décrite sur ce site.

Reste maintenant à souder les composants cms.

|

|

|

|

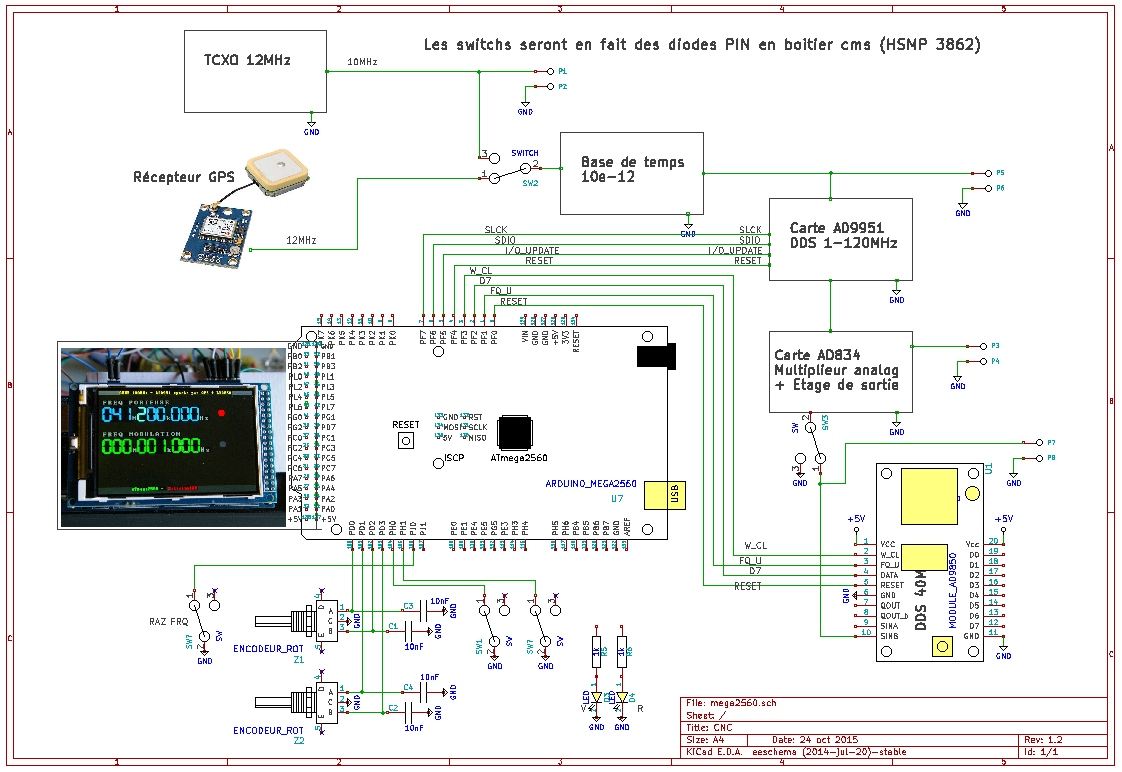

40 EVOLUTION

25 août 2015:

Je suis en train de faire évoluer cette réalisation. Un nouveau projet va voir le jour qui fera l'objet d'un nouvel article. Je vous laisse découvrir sur ce schéma en quoi cela consistera : Un générateur de porteuse de fréquence hyper précise modulable par un second signal synthétisé. Le tout orchestré par une carte ATmega2560 et un affichage TFT couleur 480x320. Je dispose de tous les composants nécessaires sauf le multiplieur analogique 500MHz (AD834) qui est en commande.

|

|

|

5 septembre 2015:

En attendant de recevoir le multiplieur analogique, j'ai, ces derniers temps, fait avancer le soft pour la carte Arduino Mega2560. Actuellement les deux génés (AD9850 et AD9951) sont correctement pilotés, l'affichage des deux fréquences est également ok. Donc le projet est très avancé.

Je me suis ensuite repenché sur la base de temps GPS. Je vous en parle plus en détail ci-dessous.

|

41 Le jitter de la base de temps GPS (suite...)

J'ai relu le "document russe", je me suis intéressé plus particulièrement au fait qu'il parle, à propos de la sortie HF du récepteur GPS NEO-7M de "bonnes" fréquences (celles ayant un faible jitter) et de "mauvaises" fréquences (toutes les autres, ayant un jitter abominable). Et il se trouve que j'ai choisi jusqu'à présent d'utiliser un signal de 10MHz qui figure parmi les "mauvaises" fréquences et qui est effectivement affublé d'un bruit de phase rendant carrément le signal flou vu avec un oscilloscope synchronisé sur une base de temps 10MHz de bonne qualité.

Pour mémoire, les bonnes fréquences sont des sous-multiples de 48MHz, inférieures (ou égales) à 24MHz, (48 MHz est la fréquence pilote au sein du récepteur GPS), c'est à dire :

- 24.000 MHz

- 16.000 MHz

- 12.000 MHz

- 8.000 MHz

- 6.000 MHz

- 4.000 MHz

- etc...

J'avais quand même choisi 10MHz parce que je voulais un "chiffre rond" pour attaquer la PLL de l'AD9951. MAIS CE N'EST PAS DU TOUT une nécessite !!

N'importe quelle fréquence peut faire l'affaire, il suffit d'adapter la formule du calcul du mot de commande dans le soft de pilotage du DDS.

Dès lors j'ai décidé d'expérimenter avec la fréquence de 12MHz (à programmer dans le NEO-7M), et un quartz 'Colpitts' 12MHz au lieu du 10MHz. Ouf ça repose les yeux à l'oscillo !

Oui mais les choses ne peuvent pas pour autant en rester là. En effet le jitter sur 10MHz était tellement important que mon étage oscillateur Colpitts à quartz était nécessaire, et efficace, divisant par au moins 100 (au pif) le jitter. Mais alors, ce doit être encore mieux pour le signal de fréquence 12MHz qui est déjà bien moins entaché par le bruit de phase ?? Et bien NON ! Dans ce cas je m’aperçois que ce bruit de phase plus faible... n'est pas (ou presque) diminué par l'oscillateur à quartz. En fait la synchronisation par couplage capacitif lâche donne un "petit coup de pouce" à chaque période qui est du même ordre de grandeur que le petit jitter résiduel. Le jitter en sortie de l'oscillateur est donc pratiquement égal à celui su signal de sychronisation ! L'oscillateur ne sert plus à rien ! Peut-on s'en passer alors ? Non, parce que ce jitter résiduel est quand même énorme compte tenu de la prétention de cet appareil à être une référence de fréquence. Autant qu'elle soit propre !

Et bien entendu je me suis assuré que ce bruit de phase résiduel n'est pas un bruit thermique, de grenaille, ou dû à un mauvais découplage d'alim... Et c'est très simple à vérifier, il suffit de déconnecter le couplage par la capa de 1pF pour que le bruit cesse immédiatement (mais alors la fréquence se met à dériver...)

Il faut donc trouver une solution. J'avais dit qu'un VCO RC n'est pas du tout assez stable et qu'il a trop tendance à se synchroniser "par sympathie" sur le signal du GPS. Reste la solution de conserver l'oscillateur à quartz (qui est apte à produire un signal de très bonne qualité) mais synchronisé d'une autre manière, par une varicap, dans une boucle PLL à filtre passe bas bien conçu. ça porte un nom, c'est un VCXO (Voltage-Controlled Crystal Oscillator). Attention : on trouve des VCXO réglables dans une plage de fréquences de 1.5MHz à 80MHz, je doute qu'ils soient à quartz !!!!!!

Donc je vais le faire moi-même !

|

|

|

|

42 VCXO maison pour PLL base de temps GPS

10 septembre 2015:

Voici donc les caractéristiques de cette nouvelle version de la base de temps:

- Exploitation d'une "bonne" fréquence (12MHz) du récepteur GPS NEO7-M à relativement faible bruit de phase.

- Génération d'un signal 12MHz "propre", sans bruit de phase, par un oscillateur colpitts à quartz 12MHz,

- Asservissement fin de la fréquence de cet oscillateur par une diode varicap pilotée par le comparateur de phase (entre le VCO et le GPS) d'un 74HC4046 suivi d'un filtre passe bas de grande période,

- Blindage soigné de l'oscillateur colpitts afin qu'il ne se synchronise pas directement sur le signal bruité en phase du GPS par couplage HF (sinon la PLL ne sert plus à rien et le résultat est désastreux)

|

|

|

|

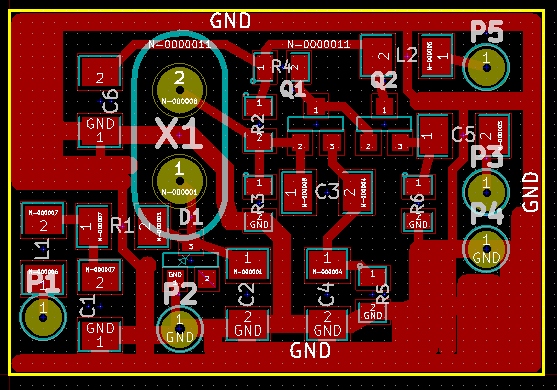

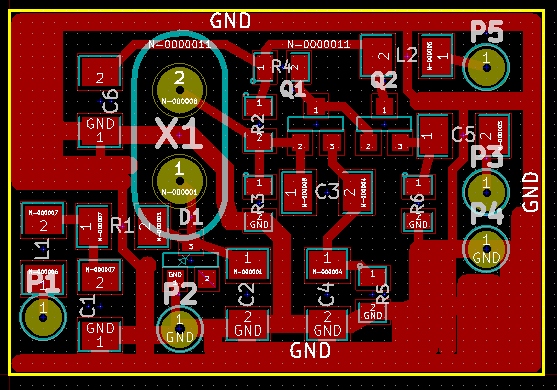

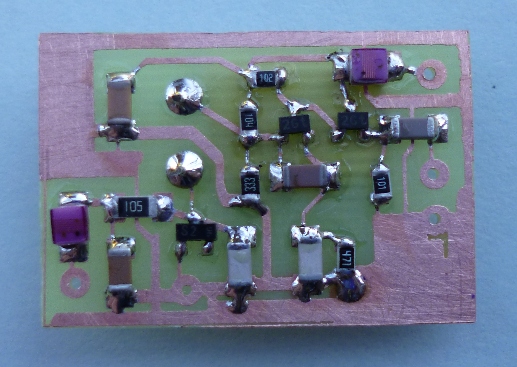

43 Le circuit imprimé :

Le circuit imprimé a été flashé avec ma machine laser. Le quartz 12MHz (qui n'est pas en CMS) se situe sur l'autre face.

|

|

|

|

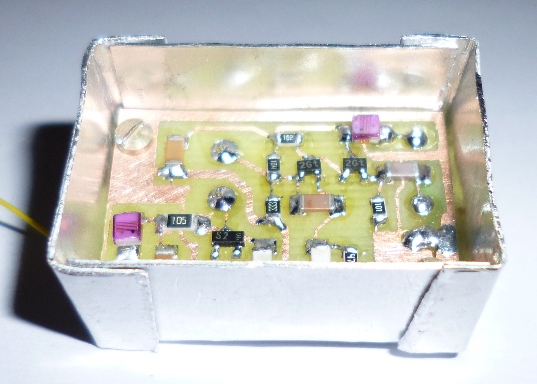

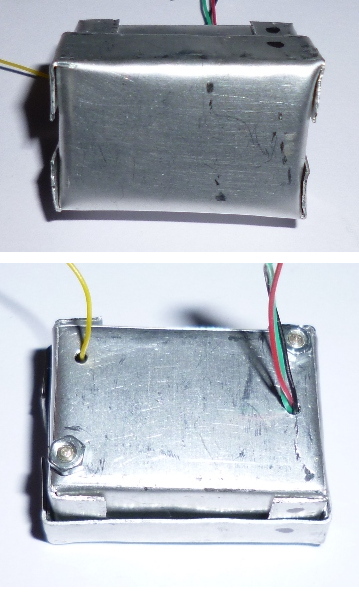

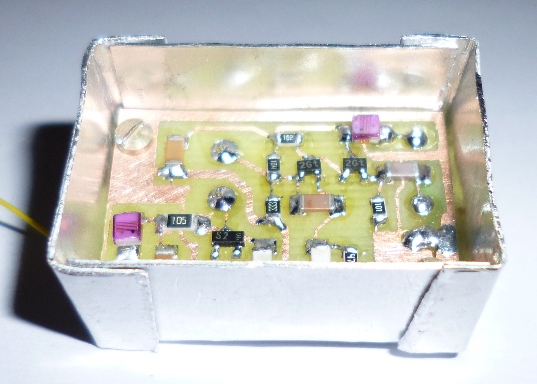

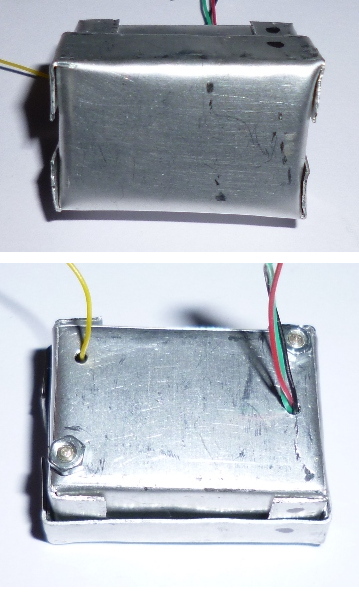

44 Le VCXO dans son boîtier blindé

Le circuit imprimé est fixé sur le fond du boîtier par deux vis de 2mm en laiton + entretoises (il faut loger le quartz dessous) assurant la conduction électrique (mise à la masse).

|

|

|

Les fils de liaison doivent être le plus court possible dans leur partie interne au boîtier sinon ils constitueront une antenne réémettant à l'intérieur ce qu'ils auront capté à l'extérieur (comme l'antenne de l'auto-radio) rendant le blindage inefficace. Le boîtier est relié à la masse du montage par les vis de fixation en laiton ainsi que par une liaison externe rajoutée. En fin ce compte c'est l'oscillo synchronisé sur une base de temps indépendante propre et fiable qui permettra de juger de l'absence de bruit de phase et donc de l’efficacité du blindage, en comparant le signal GPS entrant et le signal 12MHz reconstitué sortant, ou bien un analyseur de spectre.

|

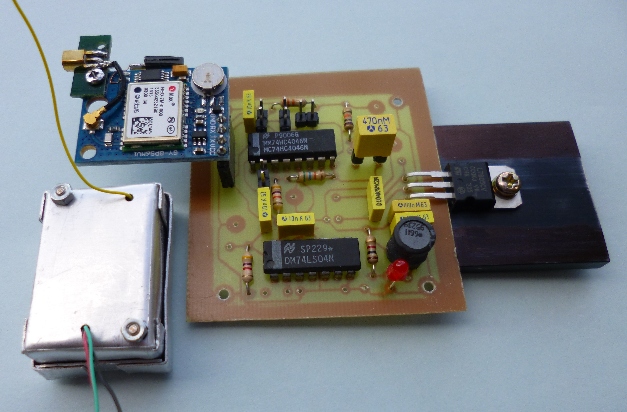

45 L'ensemble de la base de temps

Seul le VCXO est enfermé dans un blindage HF (contre les perturbations entrantes) en alu. Bien entendu l'ensemble du générateur sera enfermé dans un boitier métallique constituant un blindage CEM contre les perturbations sortantes cette fois qui pourraient affecter l'environnement. Je rappelle qu'en VHF le moindre bout de fil constitue un antenne relativement efficace. A ce sujet j'ai ajouté quelques liens vers des sites traitant des CEM au bas de cet article.

|

|

|

13 septembre 2015:

Ce schéma a été modifié plusieurs fois ces derniers jours, suite à maints et maints tests et mesures concernant la qualité de la synchronisation, la pureté des signaux, y compris du signal de sortie synthétisé par l'AD9951. Ce dernier sera situé sur une carte à part, avec ses propres alims +5V, +3V3 et +1V8. Dés lors la liaison entre cette carte base de temps et la la carte du synthé AD9951, liaison qui transmet le signal d'horloge 12MHz, doit se faire par un câble blindé HF reliant les masses au plus près des circuits 74LS04 (pin 8) d'un côté et AGND de l'AD9951 (pin7) sous peine de se retrouver avec une boucle de masse rayonnant du 12MHz qui se retrouverait sur le signal de sortie. Tous les autres fils actifs au sein d'une même carte doivent être le plus courts possible, et il faut éviter tout couplage par retours de masse communs. Ne perdons pas de vue que le 12MHz d'horloge se trouve dans la gamme de fréquences synthétisées, donc une fois que la pollution 12MHz entre dans un étage on ne peut plus la filtrer pour s"en débarrasser.

|

46 Le circuit imprimé de la base de temps

14 septembre 2015:

Le dessin du circuit imprimé est fait, il ne reste plus qu'à le flasher.

Les grosses pastilles jaunes reliées à GND correspondent à des trous qui accueilleront des vis de 2mm servant à fixer un plan de masse de toute la surface du circuit, à une distance de quelques mm au dessous. Un circuit double face aurait pu convenir également, mais les capacités rapportées auraient été plus importantes du fait de la distance beaucoup plus faible ainsi que par la nature du diélectrique autre que l'air.

|

|

|

|

47 ça avance...

22 septembre 2015:

Tout doucement... Faut dire que je ne fais pas que ça de mon temps libre, par exemple je viens de remplacer une fenêtre de toit de 1,50m x 1,50m...

|

|

|

|

48 Les essais ne devraient pas tarder

Comme d'habitude maintenant, le circuit a été flashé par ma machine laser. J'ai conservé une bande de cuivre reliée à la masse en bordure de carte simplement en appliquant une bande de scotch juste avant la gravure au perchlo.

|

|

|

|

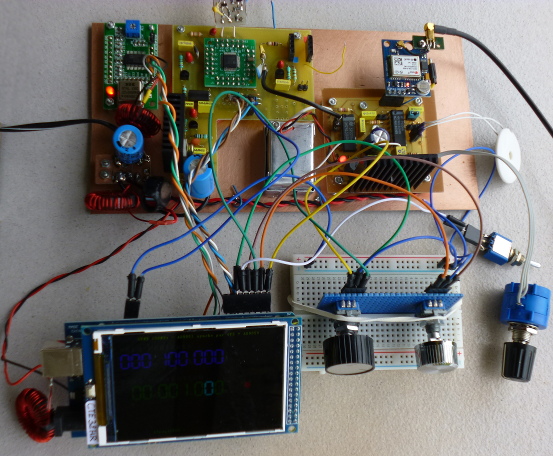

49 Toutes les cartes fonctionnent

|

Toutes les cartes sont interconnectées et fixées sur un plan de masse. La photo ayant été prise en extérieur, l'affichage sur le LCD vu de biais est bien peu visible. Bientôt tout cela sera placé dans un joli coffret métallique alu vert.

|

30 septembre 2015:

Maintenant que toutes les carte sont assemblées sur un grand circuit vierge faisant office de plan de masse, que les liaisons des signaux s'effectuent par câbles blindés et que les alimentations sont proprement découplées (selfs sur tores + capas) les signaux générés sont impeccables, tant le signal principal généré par le DDS AD9951 piloté par GPS que le signal secondaire généré par le DDS AD9850.

Entre temps j'ai acquit une horloge atomique de référence au rubidium (d'occasion à un prix très abordable sur eBay). C'est dire que question fréquence je vois nettement ce qui se passe.

A propos des horloges atomiques au Rubidium :

- Une horloge atomique, ce n'est PAS une horloge nucléaire. Ce qui est mis à profit dans une horloge atomique, c'est une fréquence de résonance des ELECTRONS de l'atome, rien à voir donc avec les constituants du noyau, pas de radioactivité au programme !

- Le Rubidium existe dans la nature sous forme de deux isotopes, le rubidium 85 stable, et le rubidium 87 très légèrement radioactif (demi-vie 47 milliards d'année) bien inférieure donc à celle du potassium 40 que nous hébergeons dans notre corps.

- Les horloges au rubidium utilisent bien l'isotope 87 radioactif, mais compte tenu de la remarque précédente, cette radioactivité n'est pratiquement pas mesurable. J'ai passé cette horloge au compteur Geiger, et je n'ai pas trouvé d'augmentation de la radioactivité par rapport à la radioctivité naturelle du lieu.

Je constate d'ors et déjà que le glissement de phase entre le signal issu du récepteur GPS NEO-7M et celui du rubidium correspond à une erreur en fréquence de 3x10E-10 ce qui est un ordre de grandeur plus important que la précision donnée pour cette horloge au rubidium (FE 5680A de chez FEI Communications, Inc.)

Toutefois je me garderai bien dès à présent d'incriminer le rubidium dont les atomes bien éduqués savent qu'ils doivent osciller à la fréquence correspondant à la transition hyperfine 5²S1/2 égale à 6.834 682 610 904 290 GHz. Quant aux satellites GPS, ils embarquent me semble-t-il des horloges semblables.

Alors où est l'erreur ? J'ai bien lu ici et là que les horloges au rubidium "vieillissent mal"... Mais de quel point de vue ? ce n'est pas précisé.

Deux autres sources d'erreurs me paraissent bien plus plausibles:

- Le récepteur GPS ne sort pas directement la fréquence de son horloge interne (64MHz) mais une fréquence reconstituée par... un circuit DDS.

- D'une manière analogue, l'horloge rubidium FE 5680A ne sort pas directement le signal 6GHz de son VFO couplé à la cavité atomiquement résonnante, ni même un 50255 MHz (après division exacte par /136), mais une fréquence (10MHz) également reconstituée par un synthétiseur qui si j'ai bien compris la doc, est un DDS. Et alors... la précision est peut-être dégradée, suivant la longueur du mot de programmation de ce DDS (nb de bits)

Quoi qu'il en soit, ne perdons pas de vue que nous obtenons une précision d'une seconde par siècle...

Mais comme je me connais, ça ne m'empêchera pas un de ces quatre d'aller choper directement le signal 6.834 682 610 904 290 GHz à l'intérieur du boîtier et de le diviser moi-même pour en avoir le cœur net.

Je vais maintenant travailler sur la partie modulateur d'amplitude. Une note d'ANALOG DEVICES (AN-423) concernant le circuit AD9850, mais sans doute transposable à l'AD9951 indique une manière très simple d'obtenir une modulation AM du signal de sortie du DDS avec un simple transistor FET utilisé en résistance dynamique variable dans le circuit (interne) de sortie. Je vais étudier ça.

|

50 Modulation AM du signal

|

En définitive le multiplieur analogique AD834 que j'avais déjà cité plus haut me donne entière satisfaction. Ses entrées différentielles symétriques s'adaptent particulièrement bien aux sorties également différentielles symétriques des DDS AD9850 et AD9851. Voici le résultat obtenu pour une porteuse de 1MHz modulée par un signal de 2kHz. Le taux de modulation est facilement réglable par un ajustable de 20K. On pourra aussi prévoir de le faire par une diode PIN pilotée par l'ATmega2560...

Je vais comme il se doit réaliser un petit circuit imprimé pour cet étage dont je publierai ici le schéma.

A suivre...

|

|

|

|

51 Schéma du modulateur

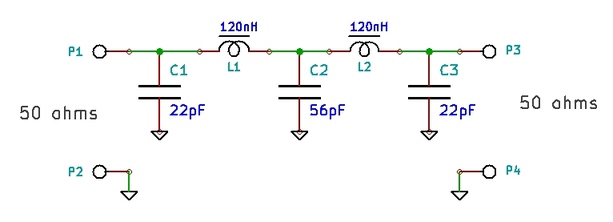

L'étage de sortie, un ampli différentiel constitué par deux transistors UHF BFR93A permet d'obtenir un signal en tension unique référencée à la masse, de bonne amplitude (1V) avec un faible bruit. Il reste à ajouter un filtre de sortie passe bas à pente raide, de type Butterworth ou Tchebychev.

|

|

|

|

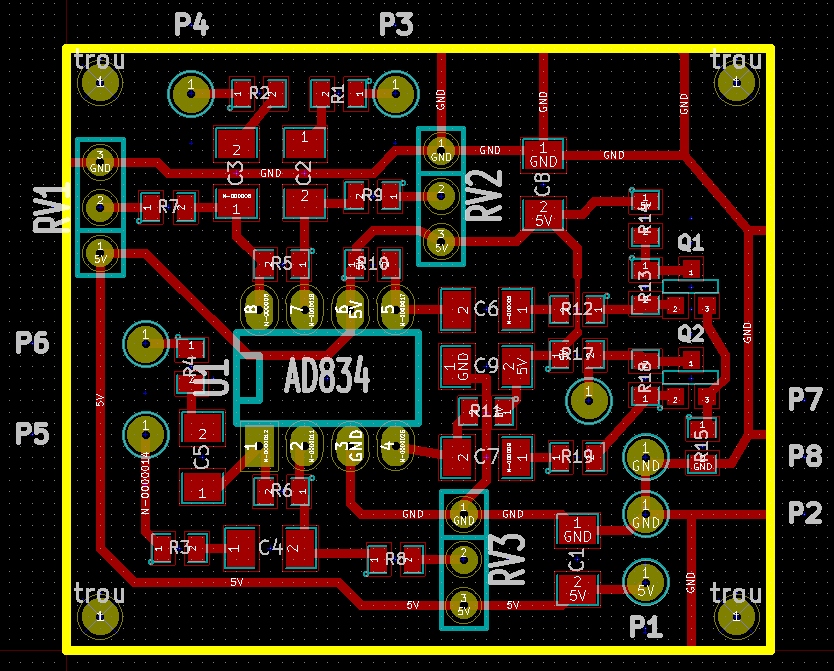

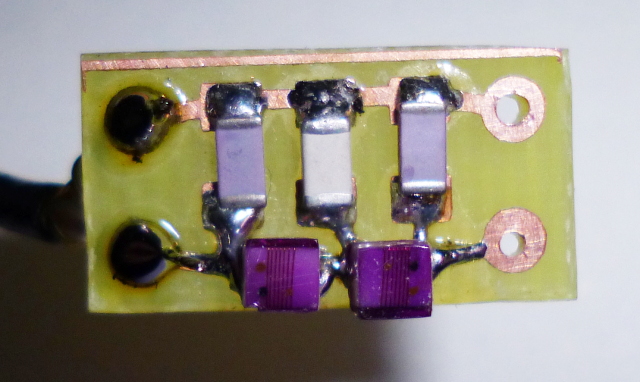

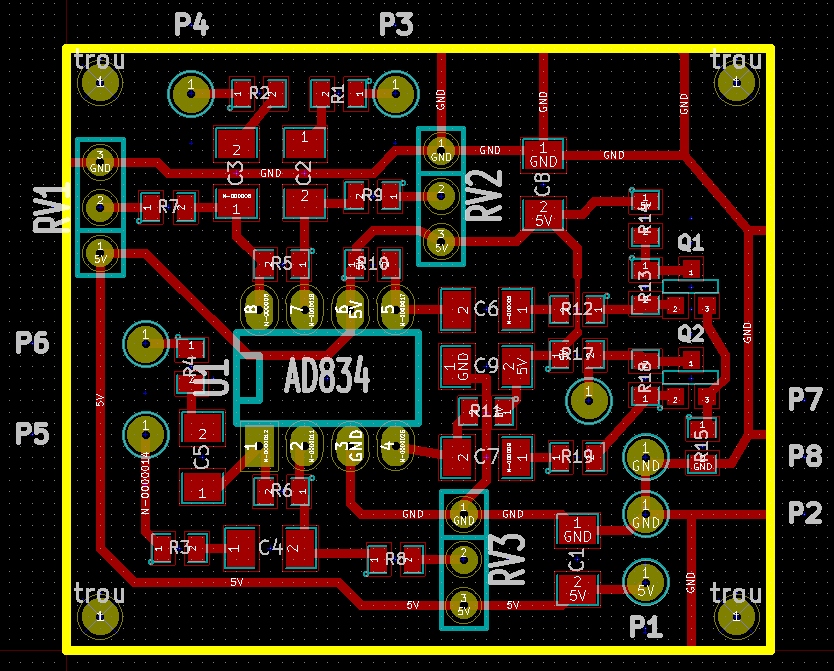

52 Le circuit imprimé du modulateur AM

|

Il est en cours de conception. Attention : Le boîtier AD834 devra être soudé côté cuivre, c'est à dire sur la même face que les composants cms. (comme si c'était un composant cms lui aussi, mais je n'en ai pas en stock dans ce format).

|

|

|

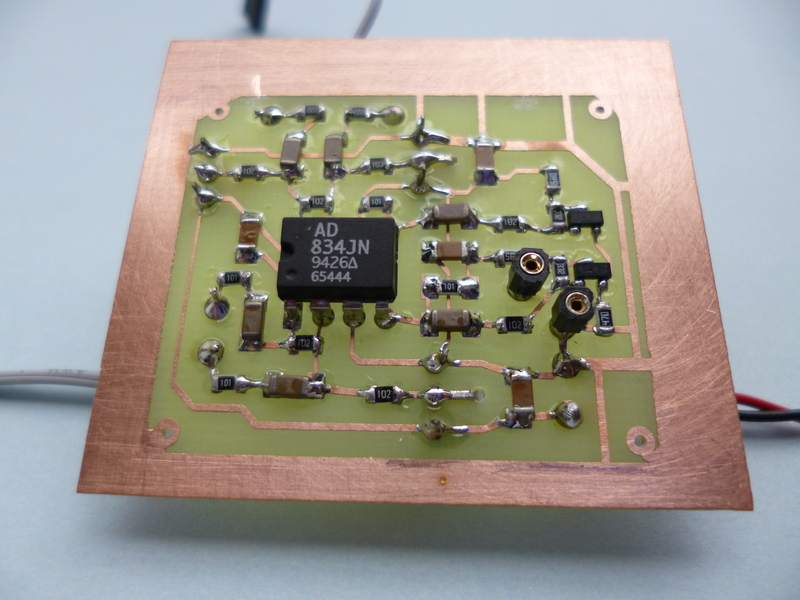

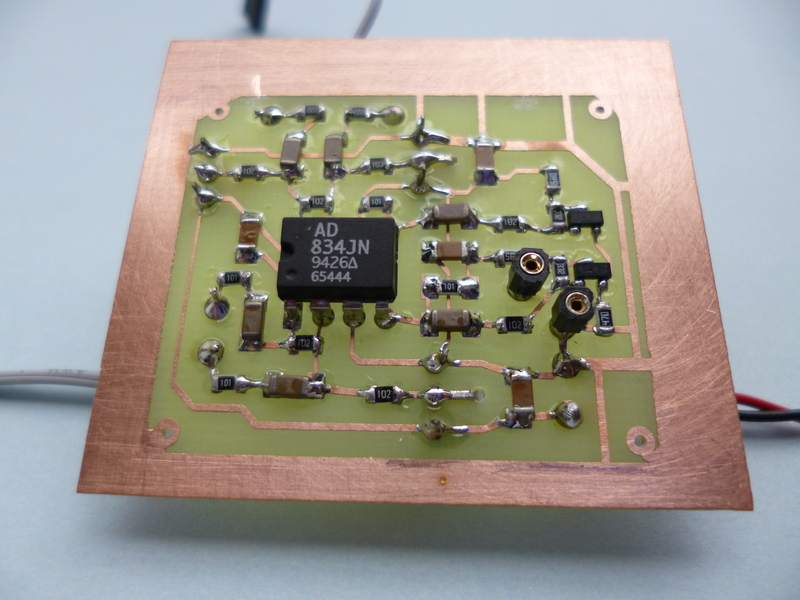

53 Modulateur terminé

|

7 octobre 2015:

Les trois ajustables 10k sont sur l'autre face. Je les remplacerai peut-être par trois tensions générées par l'ATmega2560 sous la forme de signaux PWM, intégrés par circuit RC.

Pour l'instant ceci fonctionne correctement.

Il est maintenant plus urgent de mettre en place un filtre de sortie de type Butterworth ou Tchebychev.

Je vous tiens au courant...

|

|

|

54 Le firmware en C pour l'ATmega2560 de l'Arduino

CODE SOURCE en c

/** Firmware pour générateur de signaux à deux DDS : AD9951 et AD9850. POUR carte Uno Mega2560 + afficheur 480x320 non tactile. par Silicium628. Ce fichier source "GeneHF_AD9951_MODUL.ino" est libre, vous pouvez le redistribuer et/ou le modifier selon les termes de la Licence Publique Générale GNU. En ce qui concerne certaines bibliothèques incluses, issues du domaine "Arduino", il faut voir au cas par cas. **/ // REMARQUE : les ports utilisés doivent être définis dans les fichiers "AD9850.h" et "AD9951.h" //================================ #define version "v3.4" //================================ #include <avr/io.h> #include <stdint.h> #include <stdlib.h> #include <util/delay.h> #include <math.h> #include "UTFT.cpp" #include "uart2560_628.c" #include <AD9951-628v6.cpp>; #include <AD9850-628v1.cpp>; //#include "timeout.h" // comprend : #define F_CPU 16000000UL // 16 MHz #define portPIN_switch PINH #define pin_switch1 0b00000001 #define pin_switch2 0b00000010 #define portPIN_RAZ PINK #define pin_RAZ 0b00000001 // Declare which fonts we will be using extern uint8_t SmallFont[]; extern uint8_t BigFont[]; extern uint8_t SevenSegNumFont[]; /**************************************************************************************************************************************************** //choisir le bon driver suivant, en fonction du type d'afficheur (tous deux des 480x320 qui se ressemblent, achetés au même fournisseur) ****** //la library correcte doit être installée dans le bon dossier ARDUINO, avec les permissions d'accès correctes ! UTFT TFT480(CTE32HR,38,39,40,41); UTFT TFT480(HX8357C,38,39,40,41); ****************************************************************************************************************************************************/ UTFT TFT480(HX8357C,38,39,40,41); AD9951 DDS_porteuse; AD9850 DDS_modulation; uint16_t x_7seg, y_7seg; uint32_t f_porteuse , memo_f_porteuse; // fréquence du signal de sortie sinusoïdal uint32_t f_modulation , memo_f_modulation; // fréquence du signal de sortie sinusoïdal uint32_t FTW_entier; uint8_t FTW_decim; uint8_t pos; // position du multiplicateur uint8_t pos_curseur_porteuse, pos_curseur_modulation; // position du curseur (pour affichage) uint8_t switches, memo_switches; // 8 bits permettant de mémoriser l'état de 8 inverseurs uint32_t pas_porteuse, pas_modulation; uint8_t etat; uint8_t depassement; uint16_t compteur1; uint16_t phase; uint32_t R3; double dP_r; uint16_t dP; uint8_t demande_calcul_porteuse, demande_calcul_modulation; float position; /** RAPPEL variables avr-gcc (vérifiable avec le .map) char 1 -128 .. 127 ou caractères unsigned char 1 0 .. 255 uint8_t 1 (c'est la même chose que l'affreux 'unsigned char') char toto[n] n int 2 -32768 .. 32767 int16_t 2 idem 'int' short int 2 pareil que int (?) unsigned int 2 0 .. 65535 uint16_t 2 idem 'unsigned int' long int 4 octets -2 147 483 648 à 2 147 483 647 int32_t 4 octets -> 32 bits ; idem long int long long int 8 octets -> 64 bits unsigned long int 4 octets -> 32 bits ; 0 .. 4 294 967 295 (4,2 x 10^9) uint32_t 4 32 bits ; idem 'unsigned long int' float 4 double ATTENTION ! 4 octets (oui, 32 bits ! et pas 64 bits (8 octets) comme en C standard) La déclaration char JOUR[7][9]; réserve l'espace en mémoire pour 7 mots contenant 9 caractères (dont 8 caractères significatifs). **/ void init_ports (void) // ports perso { // 0 = entree, 1=sortie ; les 1 sur les pins en entrees activent les R de Pull Up (tirage à VCC) DDRD = 0b11110000; PORTD = 0b00001111; DDRF = 0b11111111; PORTF = 0b00000000; DDRH = 0b11111100; PORTH = 0b00000011; DDRJ = 0b11111110; // PJ0 = RXD3 - PJ1 = TXD3 (attention c'est PJ1 qui est au bord du connecteur sur la carte Arduino mega2560) PORTJ = 0b00000001; DDRK = 0b11111110; PORTK = 0b00000001; // REMARQUE : les ports utilisés doivent être définis dans les fichiers "AD9850.h" et "AD9951.h" } void int_EXT_setup() { // voir 15. External Interrupts (ATmega2560.pdf p:109) EICRA |= 0b00001010; // bits[1,0] = 10 -> int0 sur front descendant; bits[3,2] = 10 -> int1 sur front descendant; - p:110 EIMSK |= 0b00000011; // bit[0]=1 -> INT0 enable ; bit[1]=1 -> INT1 enable - parag 15.2.3 EIMSK - p:111 } void timer3_setup() // Pour { cli(); TIMSK3 = 0b00000010; // Bit 1 – OCIE3A: Timer/Counter1, Output Compare A Match Interrupt Enable - p:161 TCCR3A = 0b00000000; // p:154 TCCR3B = 0b00001011; // prescaler = 1/64 - CTC mode - p:156 et tableau p:157 OCR3A = 250; // compare match register - fixe la période - 16MHz/64/250 = 1kHz sei(); } void init_variables(void) { demande_calcul_porteuse = 0; demande_calcul_modulation = 0; // f_porteuse = 100000; // f_modulation = 1000; f_porteuse = 12000000; f_modulation = 0; pos_curseur_porteuse = 5; pos_curseur_modulation = 2; pas_porteuse = 10000; switches =0; memo_switches =0; pas_modulation = 10; // adjust = 128; phase = 0; compteur1 =0; depassement =0; x_7seg =0; y_7seg =0; } ISR (INT0_vect) { //interruption sur front descendant sur l'entree Int0 // declenchee par la rotation du codeur_ROT (1) -> +/-frequence etat = PIND & 0b00000100; if ( (switches & 0b00000001) == 0) { if (etat == 0b00000100) { if (f_porteuse >= pas_porteuse) {f_porteuse -= pas_porteuse;} } else { if ( (f_porteuse+pas_porteuse) <= 120000000) {f_porteuse += pas_porteuse;} if ( (f_porteuse+pas_porteuse) > 120000000) {f_porteuse = 120000000;} } demande_calcul_porteuse = 1; } else { if (etat == 0b00000100) { if (f_modulation >= pas_modulation) {f_modulation -= pas_modulation;} } else { if ( (f_modulation+pas_modulation) <= 40000000) {f_modulation += pas_modulation;} if ( (f_modulation+pas_modulation) > 40000000) {f_modulation = 40000000;} } demande_calcul_modulation = 1; } } ISR (INT1_vect) { //interruption sur front descendant sur l'entree Int1 // declenchee par la rotation du codeur_ROT (2) -> pas uint8_t n; etat = PIND & 0b00001000; if ( (switches & 0b00000001) == 0) // saisie curseur porteuse { if (etat == 0) { if (pos_curseur_porteuse > 1) {pos_curseur_porteuse--;} } else { if (pos_curseur_porteuse < 9) {pos_curseur_porteuse++ ;} } pas_porteuse=1; for (n=1; n<pos_curseur_porteuse; n++) { pas_porteuse *=10; } demande_calcul_porteuse = 1; } else // saisie curseur modulation { if (etat == 0) { if (pos_curseur_modulation > 1) {pos_curseur_modulation--;} } else { if (pos_curseur_modulation < 8) {pos_curseur_modulation++ ;} } pas_modulation=1; for (n=1; n<pos_curseur_modulation; n++) { pas_modulation *=10; } demande_calcul_modulation = 1; } } ISR(TIMER3_COMPA_vect) { // ajustement de la fréquence par glissement de phase. // ici 1kHz // portTEST ^= pin_TEST1; compteur1++; if (compteur1 >= 100) { // ici 10Hz // ici on fait des sauts de phase (sauts dans le futur), c'est à dire qu'on raccourci la durée de la période compteur1=0; DDS_porteuse.out_POW(phase); phase +=dP ; } } void trace_ecran() { TFT480.setColor(10, 10, 5); TFT480.fillRect(0, 14, 479, 309); trace_entete(); efface_pannel_porteuse(); efface_pannel_bas(); } void trace_entete() { TFT480.setColor(64, 64, 64); TFT480.fillRect(0, 0, 479, 13); // bandeau en haut TFT480.setColor(30, 30, 30); TFT480.fillRect(0, 300, 479, 319); // bandeau en bas // TFT480.setBackColor(64, 64, 64); TFT480.setColor(255,255,255); TFT480.print("GENE 120MHz - AD9951 syncho par GPS + AD9850", CENTER, 1); // TFT480.setBackColor(64, 64, 64); TFT480.setColor(255,255,255); TFT480.print(version, 5, 300); TFT480.setColor(255,255,255); TFT480.print("ATmega2560 - ", 100, 300); TFT480.setColor(255,255,255); TFT480.print("Silicium628", 210, 300); } void TFT_aff_ICI() { TFT480.setFont(BigFont); TFT480.setColor(255,255,255); TFT480.print("ICI", 0, 220); } void TFT_affiche_chiffre_7seg(uint8_t num) { TFT480.setFont(SevenSegNumFont); TFT480.printNumI(num, x_7seg, y_7seg); } void TFT_aff_nb_form3 (uint32_t valeur, uint8_t nb_chiffres, uint8_t curseur, uint8_t R, uint8_t G, uint8_t B) { //affiche un nombre en representation decimale en separant les groupes de 3 chiffres unsigned char r ; char tbl[7]; uint8_t i; curseur=nb_chiffres +1 -curseur; for (i=1; i<=nb_chiffres; i++) { r=valeur % 10; // modulo (reste de la division) valeur /= 10; // quotient tbl[i]=r; } for (i=1; i<= nb_chiffres; i++) { TFT480.setColor(R,G,B); if (i==curseur) { TFT480.setColor(0,250,250); } TFT_affiche_chiffre_7seg(tbl[nb_chiffres +1 -i]); x_7seg+=30; uint8_t m, k, u; m =nb_chiffres-6; k =nb_chiffres-3; u =nb_chiffres; //if (i== 3) if (i== m) { TFT480.setFont(BigFont); TFT480.setColor(100,100,100); TFT480.print("M",x_7seg, y_7seg+30); x_7seg+=15; } //if (i== 6) if (i== k) { TFT480.setFont(BigFont); TFT480.setColor(100,100,100); TFT480.print("k",x_7seg, y_7seg+30); x_7seg+=15; } //if (i== 9) if (i== u) { TFT480.setFont(BigFont); TFT480.setColor(100,100,100); TFT480.print("Hz",x_7seg, y_7seg+30); } } } void affiche_frequence_porteuse(uint8_t R, uint8_t G, uint8_t B) { uint8_t x0=10; uint8_t y0=20; TFT480.setBackColor(0, 0, 0); TFT480.setColor(100,160,230); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("FREQ PORTEUSE", x0, y0); // Etiquette x_7seg = x0; y_7seg = y0+20; uint8_t p2; p2 = pos_curseur_porteuse; if ((switches & 0b00000001) == 0b00000001) {p2=0;} // pour ne pas afficher la surbrillance du "curseur" si le mode de saisie en cours concerne l'autre fréquence TFT_aff_nb_form3 (f_porteuse, 9, p2, R, G, B); } void affiche_frequence_modulation(uint8_t R, uint8_t G, uint8_t B) { uint8_t x0=10; uint8_t y0=110; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("FREQ MODULATION", x0, y0); x_7seg = x0+30; y_7seg = y0+20; uint8_t p2; p2 = pos_curseur_modulation; if ((switches & 0b00000001) == 0) {p2=0;} // pour ne pas afficher la surbrillance du "curseur" si le mode de saisie en cours concerne l'autre fréquence TFT_aff_nb_form3 (f_modulation, 8, p2, R, G, B); } /* void affiche_adjust() { uint8_t x0=10; uint8_t y0=215; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("Adj FRQ", x0, y0); x1 = x0+120; y1 = y0; uint8_t p2; p2=0; // pour ne pas afficher la surbrillance du "curseur" TFT480.setColor(0,255,0); TFT480.print(" ", x1, y1); TFT480.printNumI(adjust-128, x1, y1); } */ void affiche_phase() { uint8_t x0=10; uint8_t y0=255; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("Phase", x0, y0); x1 = x0+100; y1 = y0; uint8_t p2; p2=0; // pour ne pas afficher la surbrillance du "curseur" TFT480.setColor(0,255,0); TFT480.print(" ", x1, y1); TFT480.printNumI(phase, x1, y1); } void efface_pannel_porteuse() { uint16_t x1, y1, x2, y2; x1=5; y1=30; x2=350; y2=100; TFT480.setColor(10, 10, 5); TFT480.fillRect(x1, y1, x2, y2); TFT480.setColor(100, 100, 100); TFT480.drawRect(x1, y1, x2, y2); } void efface_pannel_bas() { uint16_t x1, y1, x2, y2; x1=5; y1=190; x2=350; y2=290; TFT480.setColor(10, 10, 5); TFT480.fillRect(x1, y1, x2, y2); TFT480.setColor(100, 100, 100); TFT480.drawRect(x1, y1, x2, y2); } void affiche_phaseOff() { uint8_t x1=340; uint8_t y1=250; TFT480.setFont(BigFont); TFT480.setColor(60,60,60); TFT480.print("phase adjust OFF", x1, y1); } void affiche_FTW_entier() { uint8_t x0=10; uint8_t y0=200; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("FTW", x0, y0); x1 = x0+100; y1 = y0; TFT480.setColor(0,255,0); TFT480.print(" ", x1, y1); TFT480.printNumI(FTW_entier, x1, y1); } void affiche_FTW_decim() { uint8_t x0=10; uint8_t y0=220; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("decim", x0, y0); x1 = x0+100; y1 = y0; TFT480.setColor(0,255,0); TFT480.print(". ", x1, y1); TFT480.printNumI(FTW_decim, x1+10 , y1); } void affiche_dP_r() { uint8_t x0=10; uint8_t y0=240; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(SmallFont); TFT480.print("dP_r", x0, y0); x1 = x0+100; y1 = y0; TFT480.setColor(200,255,0); TFT480.print(" ", x1, y1); TFT480.printNumF(dP_r,5, x1, y1); } void affiche_dP() { uint8_t x0=10; uint8_t y0=255; uint8_t x1; uint8_t y1; TFT480.setBackColor(0, 0, 0); TFT480.setColor(150,150,150); // couleur de l'étiquette uniquement TFT480.setFont(BigFont); TFT480.print("dP", x0, y0); x1 = x0+100; y1 = y0; TFT480.setColor(255,0,0); TFT480.print(" ", x1, y1); TFT480.printNumI(dP, x1, y1); } /** Le message à transmettre au module NEO-7M peut-être affiché par u-center -ouvrir le fenêtre Messages (par F9 ou menu View / Messages View) -choisir dans la liste la fonction à programmer (ici: UBX / CFG(config)/ TP5(Timepulse5) -puis dans la liste déroulante qui apparait alors dans la partie droite de la fenêtre 'Messages, selectionner '0 - TIMEPULSE' -cocher les options qui vont bien (voir page sur mon site) -le message à transmettre s'affiche alors dans le cadre au dessous. pour UBX-CFG(config)-TP5(Timepulse5) envoyé par u-center : B5 62 06 31 20 00 00 01 00 00 32 00 00 00 01 00 00 00 00 1B B7 00 00 00 00 00 00 00 00 80 00 00 00 00 6F 00 00 00 4C 95 B5 62 c'est l'entete toujours la même Nous allons transmettre ces 40 octets au module NEO-6M avec l'USART de l'ATmega, ce qui nous permettra pas la suite de nous passer du programme u-center **/ void config_NEO_7M_GPS() { //configure le recepteur GPS NEO-7M afin qu'il génère un signal 12MHz // ce qui n'est pas le cas par défaut (1 Hz) uint8_t i; uint8_t paquet[]={0xB5,0x62,0x06,0x31,0x20,0x00,0x00,0x01,0x00,0x00,0x32,0x00,0x00,0x00,0x01,0x00,0x00,0x00,0x00, 0x1B,0xB7,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x80,0x00,0x00,0x00,0x00,0x6F,0x00,0x00,0x00,0x4C,0x95 }; for (i=0; i<40; i++) { USART_TxByte(paquet[i]); // utiliser TXD3 (se configure dans le fichier usart2560_628.c) } } // =================================================================================================================================================== void setup() { // randomSeed(analogRead(0)); init_ports(); USART_Init(); TFT480.InitLCD(); TFT480.setFont(SmallFont); TFT480.clrScr(); init_variables(); int_EXT_setup(); timer3_setup(); // ATTENTION : pour l'AD9951, faire le reset AVANT l'init parce que le reset efface tout. DDS_porteuse.reset(); // DDS_porteuse.set_ref_clk(20000000, 20); // cas du TCXO 20MHz // DDS_porteuse.set_ref_clk(10000000, 20); //cas du GPS à 10MHz DDS_porteuse.set_ref_clk(12000000, 20); // cas du GPS à 12MHz DDS_porteuse.DDS_init(); DDS_modulation.reset(); trace_ecran(); affiche_leds(); config_NEO_7M_GPS(); sei(); // enable interruptions demande_calcul_porteuse = 1; demande_calcul_modulation = 2; // le AD9850 est un peu dur d'oreille au départ, il faut lui dire deux fois... (?) } void affiche_led_verte(uint8_t s) { if(s==1) { TFT480.setColor(0,255,0); // vert TFT480.fillCircle(410, 240, 10); // allume la "led" (cercle) } else { TFT480.setColor(40,40,40); // gris TFT480.fillCircle(410, 220, 10); // éteint la "led" (cercle) } } void affiche_leds() { if ( (switches & 0b00000001) == 0) { TFT480.setColor(0,255,0); // vert TFT480.fillCircle(380, 62, 10); // allume la "led" (cercle) rouge en haut TFT480.setColor(40,40,40); // gris TFT480.fillCircle(380, 152, 10); // éteint la "led" (cercle) rouge au milieu } else { TFT480.setColor(40,40,40); // gris TFT480.fillCircle(380, 62, 10); // éteint la "led" (cercle) rouge en haut TFT480.setColor(0,255,0); // vert TFT480.fillCircle(380, 152, 10); // allume la "led" (cercle) rouge au milieu } if ( (switches & 0b00000010) == 0) { if (depassement == 1) {TFT480.setColor(255,255,0);} else {TFT480.setColor(0,255,0); } TFT480.fillCircle(380, 260, 10); // allume la "led" (cercle) verte ou jaune en bas } else { efface_pannel_bas(); affiche_phaseOff(); TFT480.setColor(255,0,0); // rouge TFT480.fillCircle(380, 260, 10); // allume la "led" (cercle) rouge en bas } } void calcul_dP() { if ( (switches & 0b00000010) == 0) { R3=f_porteuse/10; // voir ISR(TIMER3_COMPA_vect) -> on modifie à la fréquence de 10Hz. dP_r=16384.0 / 100; dP_r *= FTW_decim; dP_r *= R3; dP_r /= FTW_entier; dP= (uint16_t) dP_r; } else { dP = 0; } } void loop() { uint8_t r1; while(1) { // memo_mode_saisie = mode_saisie; memo_switches = switches; // mode_saisie = portPIN_switch & pin_switch1; // mode_saisie = 0 ou 1 suivant la position du switch1 // if ((portPIN_switch & pin_switch2) == 0) mode_saisie = 3; // =2 if ((portPIN_switch & pin_switch1) == pin_switch1) { switches |= 0b00000001; } else { switches &= 0b11111110; } if ((portPIN_switch & pin_switch2) == pin_switch2) { switches |= 0b00000010; } else { switches &= 0b11111101; } calcul_dP(); if (memo_switches != switches) { affiche_leds(); affiche_frequence_porteuse(0, 100, 255); // pour raffraichier la surbrillance des curseurs sur la bonne ligne de saisie. affiche_frequence_modulation(200, 200, 0); if ((switches & 0b00000010) == 0) { efface_pannel_bas(); if (depassement == 0) { affiche_FTW_entier(); affiche_FTW_decim(); affiche_dP_r(); affiche_dP(); } } } if(demande_calcul_porteuse > 0) { demande_calcul_porteuse = 0; depassement = DDS_porteuse.calcul_FTW(f_porteuse, &FTW_entier, &FTW_decim); // effectue le calcul de TFW et retourne le reste de la division _delay_ms(1); if ( (switches & 0b00000010) == 0) { affiche_leds(); efface_pannel_bas(); if (depassement == 0) { affiche_FTW_entier(); affiche_FTW_decim(); affiche_dP_r(); affiche_dP(); } } DDS_porteuse.out_FTW(); _delay_ms(1); affiche_frequence_porteuse(0, 100, 255); _delay_ms(1); } if(demande_calcul_modulation > 0 ) { demande_calcul_modulation --; DDS_modulation.calcul_FTW(f_modulation); DDS_modulation.out_FTW(); _delay_us(10); affiche_frequence_modulation(200, 200, 0); _delay_us(10); } if((portPIN_RAZ & pin_RAZ) == 0) // RAZ des fréquences sur appui de l'encodeurs rotatif du haut (qui comprend un switch) { if ( (switches & 0b00000001) == 0) {f_porteuse =0; demande_calcul_porteuse += 1; } else {f_modulation =0; demande_calcul_modulation = 1;} if ((switches & 0b00000010) == 0) { // soft reset switches == 0; TFT480.clrScr(); TFT480.setColor(30, 30, 30); TFT480.fillRect(0, 150, 479, 200); // bandeau TFT480.setColor(255,0,0); TFT480.print("SOFT RESET", CENTER, 160); _delay_ms(1000); TFT480.clrScr(); setup(); } } _delay_ms(1); } }

|

|

Mon fichier "AD9951-628v6.cpp" (bibliothèque de fonctions en C pour piloter le DDS AD9951) ;

Son homologue pour le AD9850 ;

|

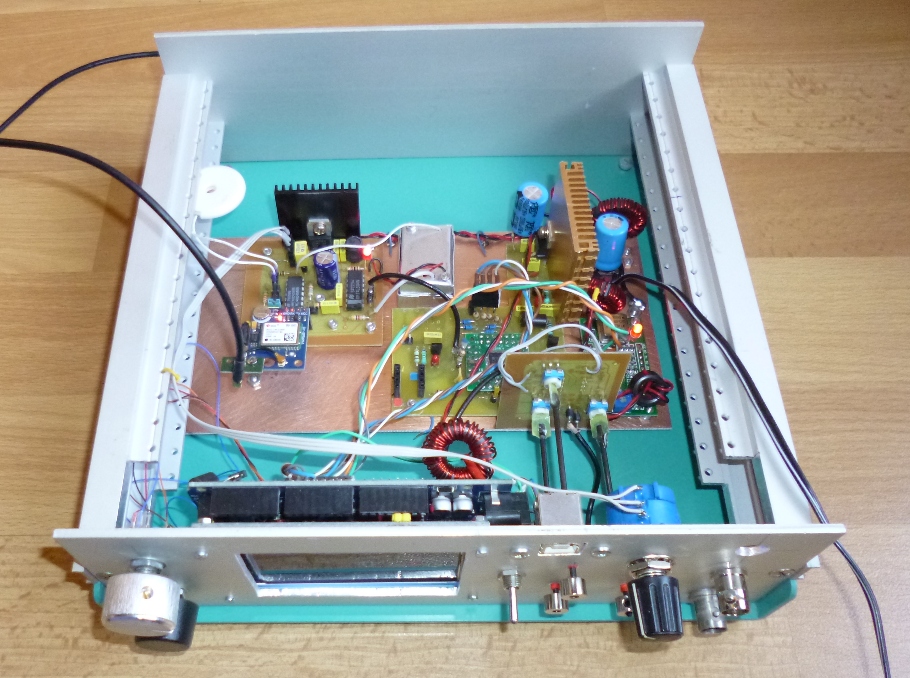

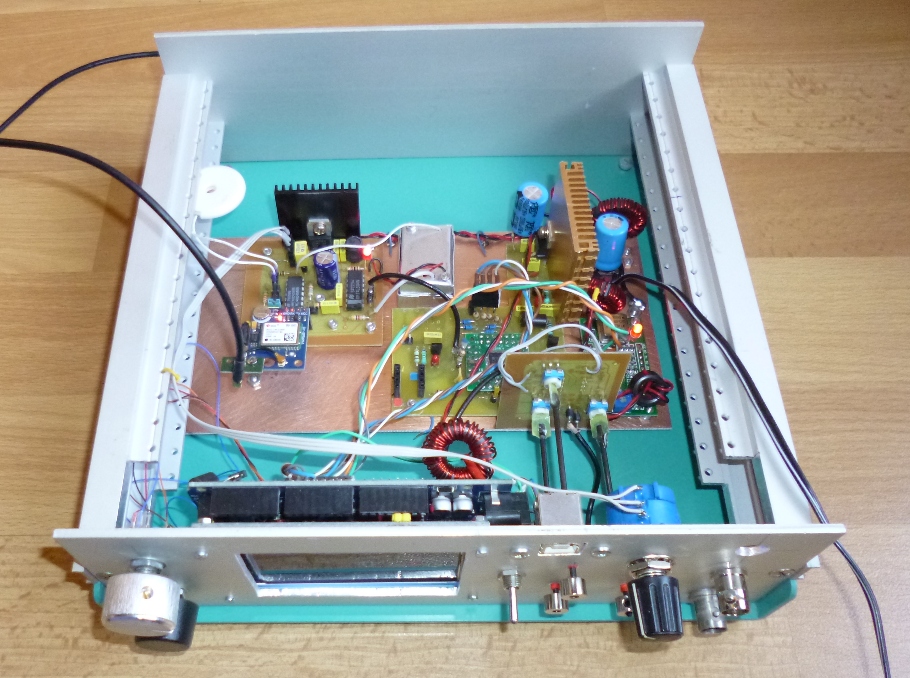

55 L'appareil dans son boîtier

22 octobre 2015:

Les principaux éléments sont installés dans un grand boîtier en alu, toutefois l'appareil n'est pas terminé pour autant.

Outre le fait qu'il reste à câbler au moins deux prises BNC de façon à sortir le signal sinus de l'AD9951 brut (non modulé) ainsi que le signal de sortie brut 12MHz du récepteur GPS, mais aussi de réaliser le filtre de sortie de type Butterworth ou Tchebychev dont je parle régulièrement (et qui, compte tenu des moyens de calculs actuels et l'utilisation de composants CMS ne devrait pas poser de problème), il reste un point important, essentiel, à résoudre. Je m'explique :

|

|

|

|

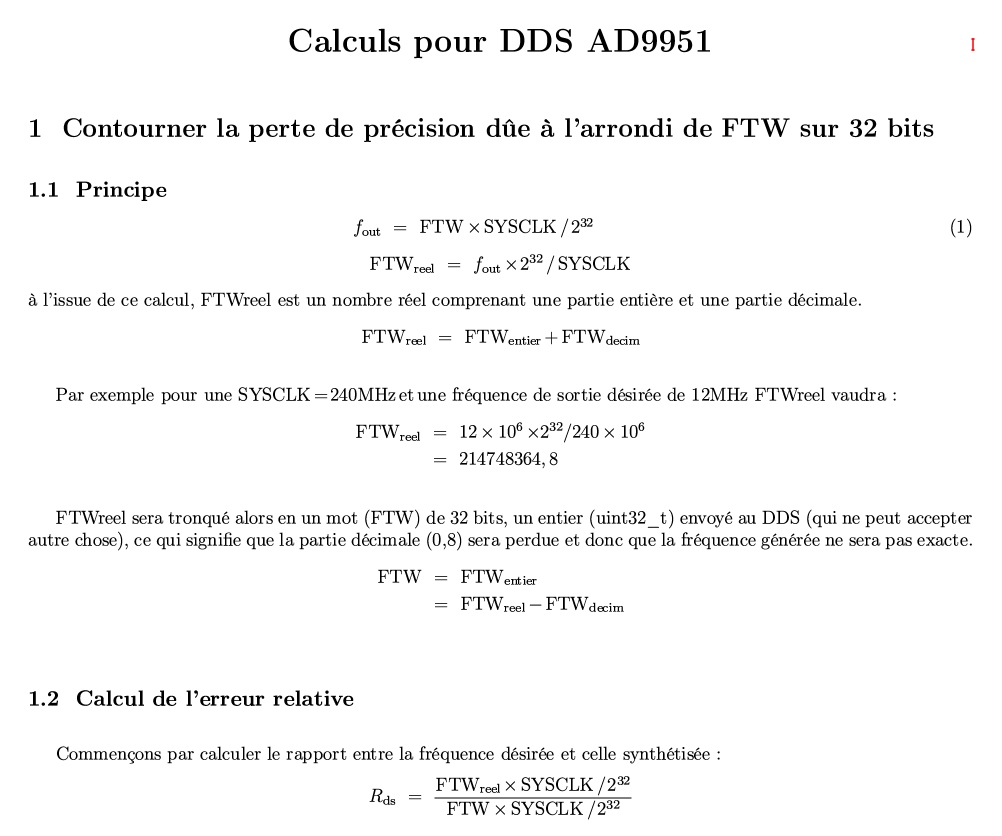

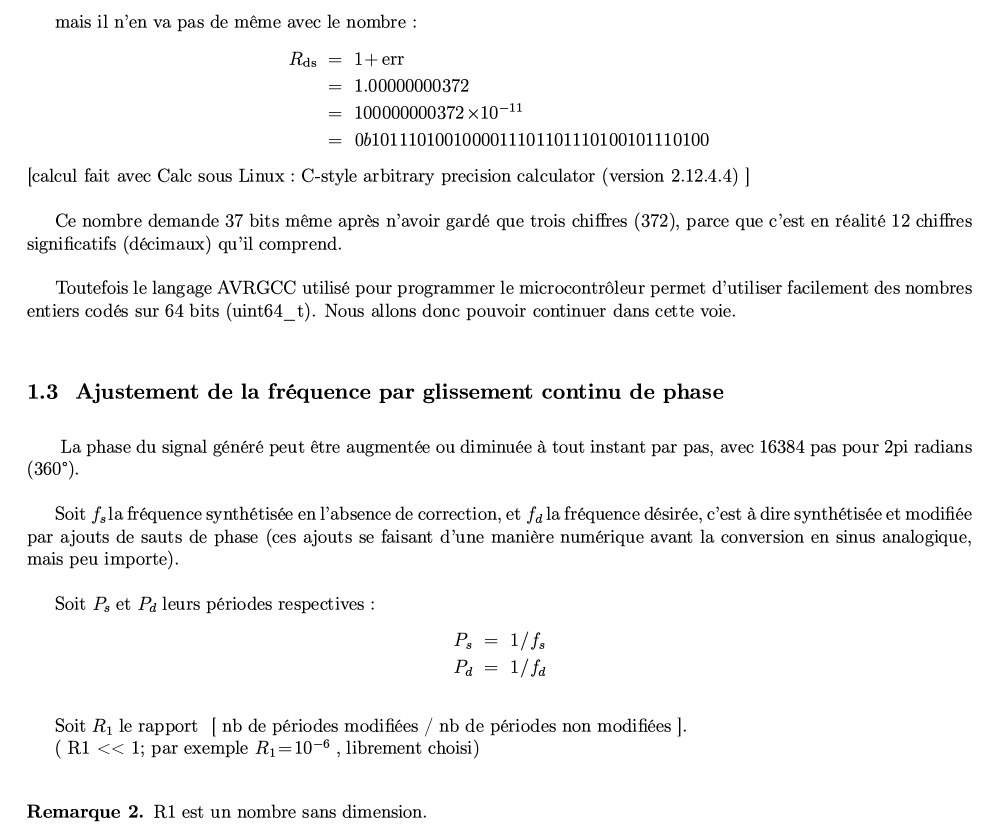

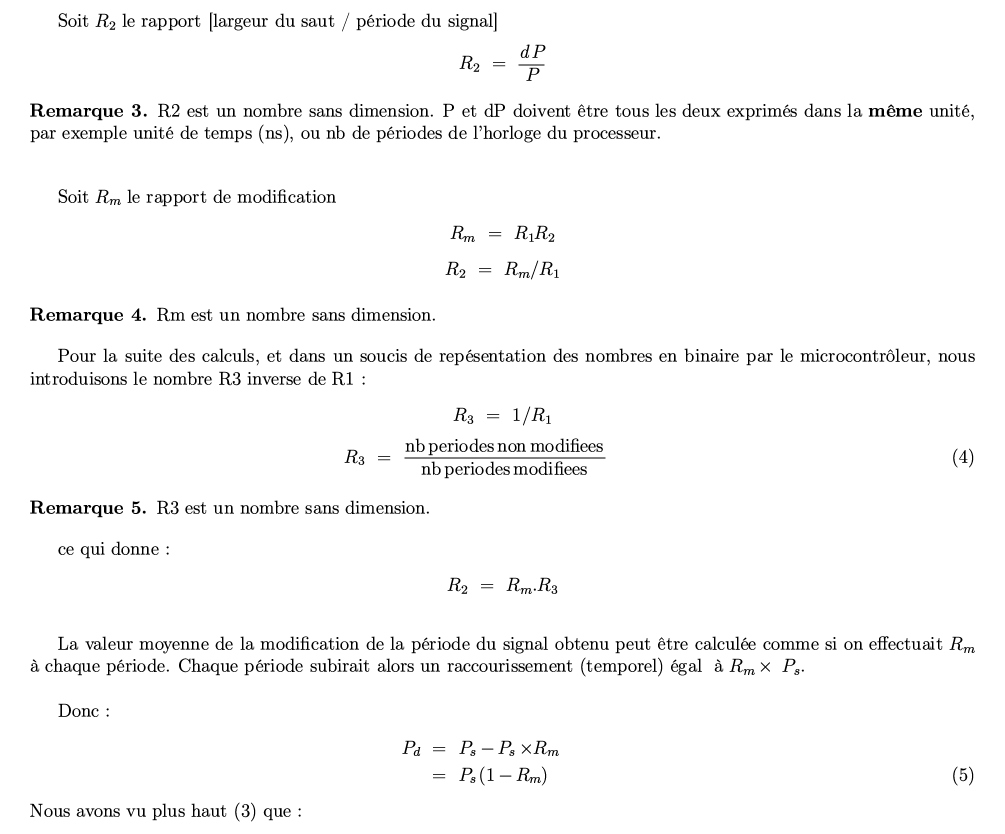

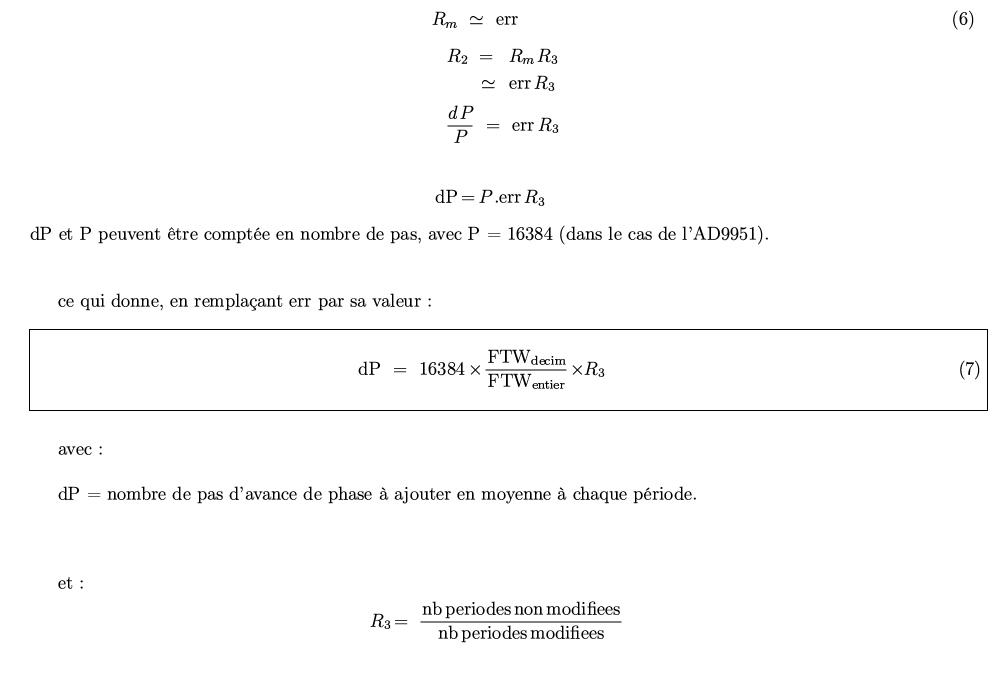

56 Précisions sur la précision

Nous avons vu que la synchronisation du signal d'horloge par un récepteur GPS permet d'obtenir une horloge dont la précision théorique est de l'ordre de 10E-12 dit-on. Mais lorsqu'on alimente un circuit DDS avec une telle horloge, ledit DDS fournit des fréquences recalculées qui ont la stabilité du GPS (pratiquement pas de dérive à long terme), mais pas la précision, cette dernière étant automatiquement perdue par le fait que le calcul dans la DDS génère une erreur, certes très très minime, certes déterministe, connue (si on se penche de très près sur le calcul...), mais différente pour chaque fréquence et très mal venue s'agissant d'un générateur de fréquence.

La solution ? Se pencher justement sur le calcul pour imaginer la parade. L'erreur de fréquence est tellement faible que l'on devrait plutôt parler de lent et régulier glissement de phase.

Le plus simple pour le mettre en évidence consiste à régler le générateur afin qu'il produise un signal de sortie de 12MHz et de comparer ce signal, à l'oscillo en bi-trace ou en Lissajous avec le signal 12MHz pilotant le DDS. Ce devrait être exactement la même fréquence mais du fait du principe même du DDS ce n'est pas le cas. Il y a glissement d'une période entière après environ 22s soit 1/22x10E6 = 3.8x10E-9 ce qui dégrade la précision d'un facteur dix par rapport à celle obtenue en comparant la fréquence du GPS à celle du rubidium (sachant que je ne sais toujours pas vraiment laquelle est la plus exacte des deux, rubidium ou GPS ??) précision qui je le rappelle était dans le pire des cas 3x10E-10. Dommage non ?

La parade pourrait consister à injecter des périodes à des moments précis (toutes les x périodes...), ce qui consiste à provoquer des sauts de phases bien peu sympathiques, ou alors à provoquer un lent et régulier glissement de phase antagoniste ce qui serait bien plus indolore. Cette seconde façon de faire semble justement bien convenir au circuit DDS puisqu'on peut piloter finement la phase du signal de sortie, comme l'explique son datasheet.

Un autre approche consisterait à ne pas garantir la fréquence des signaux sinus avec une telle précision, et en contrepartie générer des fréquences "rondes" par divisions exactes du 12MHz (avec des diviseurs TTL LS ou une PLL avec diviseur programmable telle le LM7001 déjà expérimenté sur ce site, ICI). Comme quoi, parfois, qui peut le moins peut le plus !!

(Remarque : 1/2³² ~= 2.3x10E-10 pour le mot de 32 bits définissant la fréquence dans le DDS, on devrait donc pouvoir faire mieux en revoyant la programmation du DDS de plus près. C'est bizarre, j'ai pourtant effectué le calcul du mot de commande sur 64 bits avant de l'appliquer au DDS). Toutefois cette précision de 2.3x10E-10 ne serait valable que pour des variations autour de la pleine échelle (240MHz en sortie du multiplieur interne) ? Je vais tirer ça au clair.

23 octobre 2015:

Voici la procédure de test que j'ai appliquée : J'ai donc réglé le générateur afin qu'il produise un signal de sortie de 12MHz et comparé ce signal, à l'oscillo avec le signal 12MHz pilotant ce DDS. Léger glissement d'une période en 22s. J'ai alors bricolé le calcul du mot de commande du DDS (voir le fichier AD9951-628v2.cpp) en ajoutant "1" (une unité) au mot FTW avant de l'envoyer au DDS. Et dés lors le glissement d'une période se fait en 1m30s, soit 90s.

Ce qui correspond cette fois à une imprécision de 1x10E-9, soit environ quatre fois mieux. Si j'ajoute (ou retranche) plus d'une unité alors le glissemment s'accentue au contraire. Preuve que le calcul est exact à... un bit près. Pas de solution exacte donc à attendre de ce côté, je vais juste voir comment se fait l'arrondi dans mon code source, au passage des uint64 vers un entier 32 bits.

|

|

24 octobre 2015:

Etant donné le constat précédent j'ai donc appliqué la solution suivante :

- calcul du mot de commande avec une précision de 1 bit supplémentaire, avec la technique dite "de virgule fixe" dont j'ai déjà parlé à propos de l'implantation de la FFT sur ATmega.

- utilisation de ce bit supplémentaire appelé ici "demi_bit" pour arrondir intelligemment le mot de commande FTW codé sur 32 bits

Le résultat est un glissement imperceptible au premier coup d’œil à l'oscillo (pour Fout = 12MHz, mais aussi pour les autres fréquences dans un rapport simple), au point qu'il faut s’asseoir sur une chaise bien confortable et observer les traces pendant plusieurs minutes pour constater le décalage progressif (entre je le rappelle le 12MHz appliqué au DDS et le 12MHz synthétisé en sortie :))

Bien, bien, on va maintenant passer le tout à l'épreuve de l'horloge atomique au RUBIDIUM. (Le modèle dont je dispose, FE-5680A fournit un signal de 10MHz). Je vous tiens au courant.

|

57 La parole est au Rubidium

|

10 novembre 2015:

Premier test donc avec le générateur au rubidium comme référence :

Je constate que le signal 12 MHz issu du récepteur GPS, outre son bruit de phase, est l'objet de petits sauts (minimes) de phase et qu'il finit par se décaler d'une période en 2mn52s, soit 172s. Ce qui nous donne un delta de 4.8x10E-10, très proche de ce que j'avais précédemment mesuré (voir #49 ci-dessus). Problème : comment savoir lequel a raison, le rubidium acheté d'occase ou le GPS ? Je me garderai bien de trancher.

Deuxième test, toujours avec le rubidium comme référence :

Je mesure que la fréquence 12MHz synthétisée par le AD9951 se décale d'une période en 64s soit un delta de 1.3x10E-9 ce qui se rapproche de l'erreur introduite par le calcul dans le DDS qui est pour cette fréquence (après arrondi correct du mot de commande de la fréquence codé sur 32 bits comme nous l'avons vu plus haut le 23 octobre 2015, voir le #56 ci-dessus) de 1x10E-9.

Cette erreur là on sait d'où elle provient, je vais réfléchir un peu plus sur la possibilité de gérer un glissement de phase doux, en gardant ce même circuit DDS 9951.

|

|

|

|

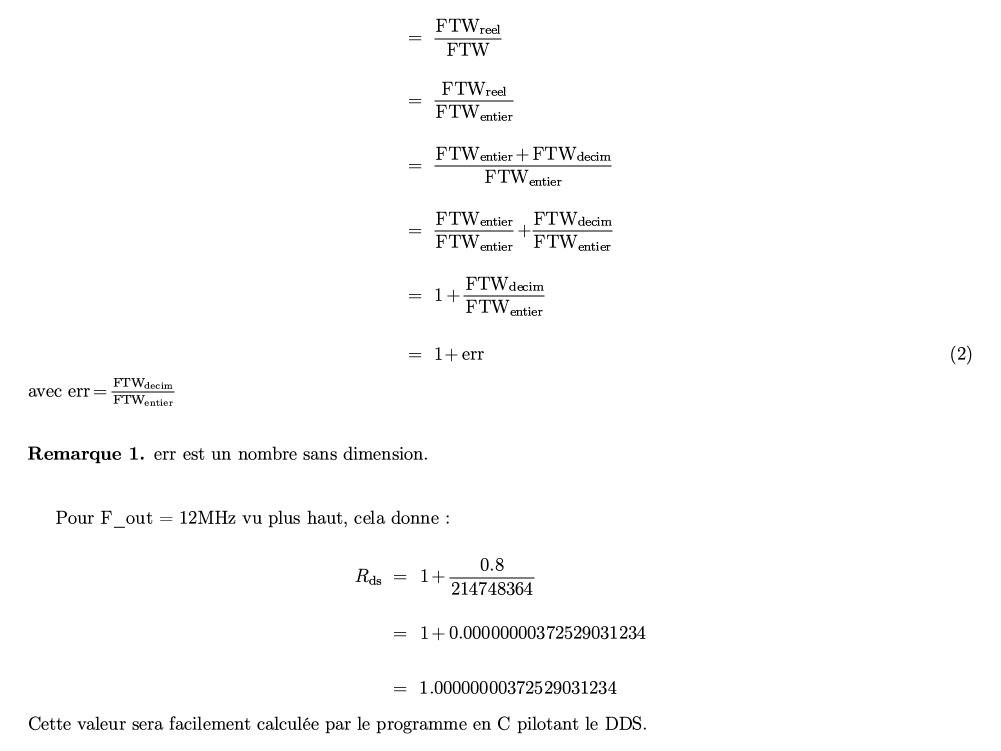

58 La fonction Phase-offset de l'AD9951

Nous voyons sur le diagramme fonctionnel de l'AD9951, dans le "DDS core" un sommateur qui ajoute un offset à la phase instantanée calculée du signal généré. Cet offset est codé sur 14 bits ce qui permet un réglage très précis. La principale application consiste à obtenir une modulation de phase du signal. Nous allons mettre à profit cette fonction pour améliorer la précision de la fréquence générée en provoquant un glissement lent et continu de la phase. Je suppose que la phase peut varier de 0 à 2pi ce qui correspondra à une période complète sans discontinuité (saut) de phase perceptible. Je vais tester ça. Je précise qu'il s'agit d'apporter une correction hyperfine de la fréquence afin de pratiquement annuler l'erreur d'arrondi de la valeur du mot de commande sur 32 bits. Cette erreur est déterministe, elle correspond au reste de la division effectuée lors du calcul de FTW. Elle dépend donc de la fréquence générée. L'ATmega 2560 nous calculera la correction à appliquer pour chaque fréquence.

|

|

|

11 novembre 2015:

Comme j'aime bien ne pas brûler les étapes lors de la conception, j'ai dans un premier temps piloté manuellement la valeur de l'offset de phase (avec le bouton encodeur rotatif correctement programmé). Je constate que le résultat est conforme à ce que j'attendais, je peux régler la phase du signal de sortie en temps réel avec une extrême précision, et sans le moindre "glitch" lors de l'envoi du mot POWO à l'AD9951, conformément à ses spécifications. On peut donc contrôler la phase en continu (plus exactement par pas discrets, certes, mais tellement fins... 2pi/16384 ) tout en gardant un signal sinusoïdal très propre. De plus le passage du mot depuis la valeur 16384 vers 0 s'effectue correctement sans saut de phase intempestif (j'avais un tout petit doute sur ce point), ce qui prouve que

l'étendue du réglage pour un mot de 14bits correspond bien à l'intervalle [0..2pi] et non pas [0..pi] ou [0..pi/2] comme on aurait pu le craindre. Ce point est essentiel si l'on veut obtenir un glissement (en occurrence l'annulation d'un glissement) de phase en continu. En résumé, l'AD9951 est un circuit très chouette !

Après quelques essais de programmation, je peux dès maintenant vous confirmer qu'avec cette technique d'ajustement logiciel fin et régulier de la phase on peut obtenir TRES SIMPLEMENT une maîtrise de la fréquence avec une précision inimaginable, en fait infinie, il suffit d'espacer ces ajustements dans le temps autant que l'on veut.

Il reste donc maintenant à faire un petit peu de math afin de calculer la valeur de ces ajustements (en durée et en espacement, donc le rapport cyclique) en fonction des "chiffres après la virgule" perdus lors de l'arrondi de la fréquence calculées sur 64bit par l'ATmega vers le mot de commande de 32 bits. Car si actuellement j'ai obtenu par tâtonnement un résultat parfait pour la fréquence synthétisée égale à celle de l'horloge (12MHz), il faut maintenant que la méthode puisse fonctionner pour toutes les cent vingt millions de fréquences synthétisables. Tiens c'est marrant, mon correcteur orthographique me souligne ATmega, et me propose... allume-gaz !!!!! Ben voyons !

|

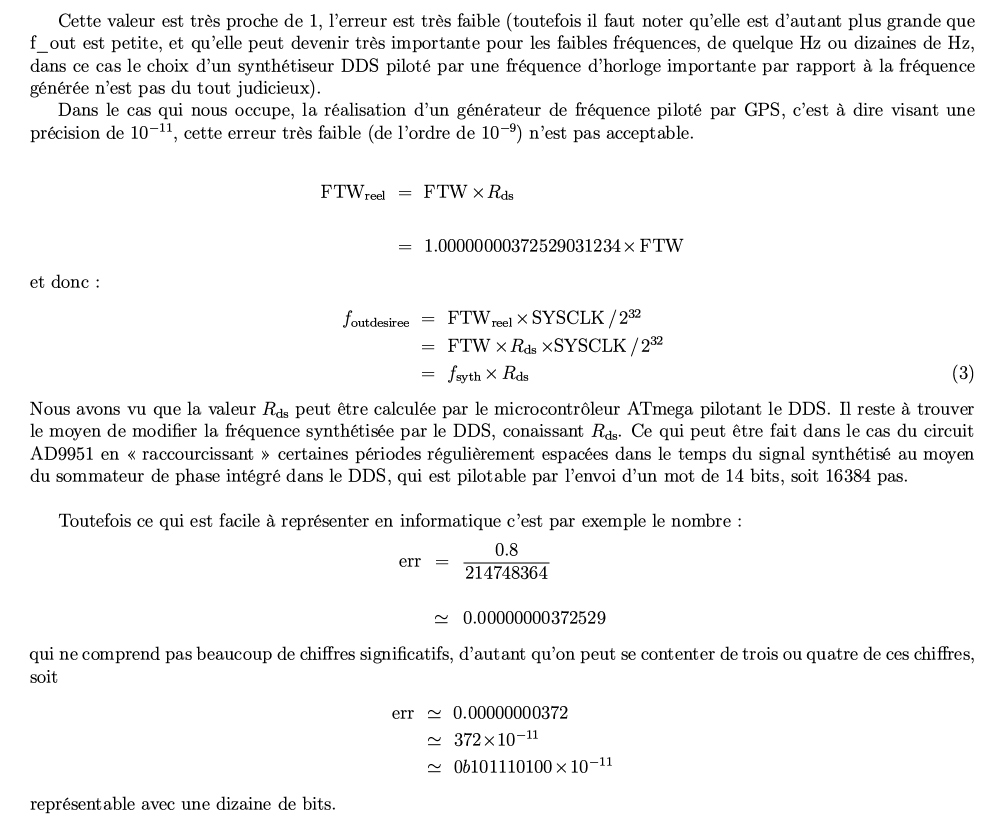

59 Calcul du glissement de phase

|

|

|

|

|

60 Application pratique :

|

18 novembre 2015:

L'implantation de ce calcul produit exactement l'effet recherché : Dans le cas de la synthèse d'un signal d'une fréquence de 12 MHz, je ne constate plus aucun glissement de phase entre le signal de sortie et le signal d'horloge issu du récepteur GPS pilotant le DDS.

Et il en va de même pour toutes les autres fréquences que j'ai testées.

Ci-contre une vue du module TFT qui affiche, en plus des fréquences de la porteuse et de la modulation, les valeurs des nouvelles fonctions.

|

|

|

2 décembre 2015:

Toutefois pour ne rien vous cacher la méthode bute sur un problème de grand entier : le codage de la fréquence et des variables intermédiaires utilisées dans le calcul, tous codés sur 64 bits (avec des uint64_t), ne permet pas de dépasser la fréquence de 42MHz. Au delà il faut plus que 64 bits. Mais je ne m'avoue pas vaincu, je compte utiliser une bibliothèque d'entiers en 128 bits (uint128_t).

4 décembre 2015:

En fait l'utilisation d'entiers 128bits s'est révélée trop lourde (à cause de l'utilisation d'une fonction "divmod" courante sous python mais inconnue du compilateur avr-gcc...)

J'ai donc revu mon calcul de façon à ne prendre en compte qu'une décimale au lieu de deux lorsque la fréquence est supérieure à 42 MHz, ce qui a pu se coder avec des uint64_t. La précision relative reste correcte (du fait que plus la fréquence désirée est grande, plus le mot de commande FTW est grand et donc le poids des décimales perdues est plus faible). Je précise que je mets toujours à jour les versions du firmware proposé ci-dessus (au #54).

|

61 En vidéo

|

|

Voici la vidéo montrant comment la figure de Lissajous (entre le signal d'horloge et le signal de sortie) se fige lorsqu'on active la compensation de phase. Même pour des fréquences qui ne sont pas dans un rapport entier, dans ce cas la figure de Lissajous est plus compliquées (plusieurs boucles entrecroisées), mais elle cesse également de tourner, ce qui est très convainquant.. L'oscillo reçoit deux signaux :

-le 12 MHz issu du quartz piloté par GPS (la sortie de ce signal se fait par une prise BNC située à l'arrière du générateur, donc non visible ici), ce signal étant (et c'est ce qui nous importe ici) celui qui constitue l'horloge de référence en entrée du circuit DDS AD9951.

-et le signal sinusoïdal généré par le circuit DDS.

Je montre tour à tour ce qui se passe pour des fréquences de :

- 12 MHz; - 10 MHz; - 8 MHz; et 6 MHz

(J'ai de mon côté testé d'autres fréquences de 10 kHz à 100 MHz...)